# CN0363

# Table of contents

| CN0363                    | 2 |

|---------------------------|---|

| CN0363 DMA Sequencer      | з |

| Files                     | з |

| Signal and Interface Pins | з |

| Theory of Operation       | 5 |

| More Information          | 6 |

| CN0363 Phase Data Sync    | 6 |

| Files                     | 6 |

| Signal and Interface Pins | 6 |

| Theory of Operation       | 7 |

| More Information          | 8 |

|                           |   |

# CN0363

CN0363 library comprises two IPs:

- CN0363 DMA Sequencer

- CN0363 Phase Data Sync

CN0363 DMA Sequencer core acts as a link between the CN0363 processing pipeline and the connected DMA controller. CN0363 Phase Data Sync assembles the raw ADC sample data into a 24-bit word and convert it to two's complement.

# CN0363 DMA Sequencer

The CN0363 Sequencer FPGA Peripheral is part of the CN0363 HDL project and is responsible to sequence the various data channels to the DMA.

## Files

|   | phase          | dma_wr            |   |

|---|----------------|-------------------|---|

|   | data           | overflow          | — |

|   | data_filtered  | dma_wr_sync       | _ |

|   | i_q            | processing_resetn | _ |

|   | i_q_filtered   |                   |   |

| _ | clk            |                   |   |

| _ | resetn         |                   |   |

| _ | channel_enable |                   |   |

|   |                |                   |   |

cn0363\_dma\_sequencer

| Name                                                                | Description                                                                 |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------|

| library/cn0363/cn0363_dma_sequencer/<br>cn0363_dma_sequencer.v      | Verilog source for the peripheral.                                          |

| library/cn0363/cn0363_dma_sequencer/<br>cn0363_dma_sequencer_ip.tcl | TCL script to generate the Vivado IP-integrator project for the peripheral. |

## Signal and Interface Pins

## phase

AXI-Stream slave - Phase data channel.

| Physical Port | Logical Port | Direction | Dependency |

|---------------|--------------|-----------|------------|

| phase_valid   | TVALID       | in        |            |

| phase_ready   | TREADY       | out       |            |

| phase         | TDATA        | in [31:0] |            |

## data

AXI-Stream slave - Sample data channel.

| Physical Port | Logical Port | Direction | Dependency |

|---------------|--------------|-----------|------------|

| data_valid    | TVALID       | in        |            |

| data_ready    | TREADY       | out       |            |

| Physical Port | Logical Port | Direction | Dependency |

|---------------|--------------|-----------|------------|

| data          | TDATA        | in [23:0] |            |

## data\_filtered

AXI-Stream slave - Filtered sample data channel.

| Physical Port       | Logical Port | Direction | Dependency |

|---------------------|--------------|-----------|------------|

| data_filtered_valid | TVALID       | in        |            |

| data_filtered_ready | TREADY       | out       |            |

| data_filtered       | TDATA        | in [31:0] |            |

## i\_q

AXI-Stream slave - Demodulated I/Q sample data channel.

| Physical Port | Logical Port | Direction | Dependency |

|---------------|--------------|-----------|------------|

| i_q_valid     | TVALID       | in        |            |

| i_q_ready     | TREADY       | out       |            |

| (i_q)         | TDATA        | in [31:0] |            |

## i\_q\_filtered

AXI-Stream slave - Filtered demodulated I/Q sample data channel.

| Physical Port      | Logical Port | Direction | Dependency |

|--------------------|--------------|-----------|------------|

| i_q_filtered_valid | TVALID       | in        |            |

| i_q_filtered_ready | TREADY       | out       |            |

| i_q_filtered       | TDATA        | in [31:0] |            |

#### dma\_wr

FIFO Write Interface master - Low-level SPI bus interface that is controlled by peripheral.

| Physical Port   | Logical Port | Direction  | Dependency |

|-----------------|--------------|------------|------------|

| dma_wr_en       | EN           | out        |            |

| dma_wr_data     | DATA         | out [31:0] |            |

| dma_wr_overflow | OVERFLOW     | in         |            |

| dma_wr_xfer_req | XFER_REQ     | in         |            |

## Ports

| on |  |

|----|--|

|----|--|

| Physical Port     | Direction | Dependency                                                  | Description                                                                              |

|-------------------|-----------|-------------------------------------------------------------|------------------------------------------------------------------------------------------|

|                   |           |                                                             | Clock - All other signals are synchronous to this clock. Bus                             |

| clk               | in        |                                                             | <pre>phase_data_data_filtered_i_q_i_q_filtered_dma_wr</pre>                              |

|                   |           |                                                             | synchronous to this clock domain.                                                        |

| resetn            | in        |                                                             | Synchronous active low reset - Resets the internal state machine of the core.            |

| overflow          | out       |                                                             | Output - The overflow signal is asserted if a overflow on the DMA interface is detected. |

| dma_wr_sync       | out       |                                                             |                                                                                          |

| channel_enable    | in [13:0] |                                                             | Input - Data channel enable sequencer output enable.                                     |

|                   |           |                                                             | Output - Reset signal for the processing pipeline Bus                                    |

| processing_resetn | out       | <pre>phase_data_data_filtered_i_q_i_q_filtered_dma_wr</pre> |                                                                                          |

|                   |           |                                                             | synchronous to this reset signal.                                                        |

# Theory of Operation

The CN0363 DMA sequencer core acts as a link between the CN0363 processing pipeline and the connected DMA controller. On one side it accepts data from the processing pipeline and on the other side it sends the data to the DMA controller. The core is only active when the DMA controller signals that it is waiting for data, when it is inactive it also asserts the processing\_resetn signal to keep the processing pipeline in reset. Since the DMA is running at a much faster clock than the output data rate from the processing pipeline the different channels are time-division-multiplexed and send one by one to the DMA controller over the dma\_wr interface.

When active the core cycles through the input channels in the following order.

- 1. phase (Reference channel)

- 2. data (Reference channel)

- 3. data\_filtered (Reference channel)

- 4. i\_q, I component (Reference channel)

- 5. i\_q, Q component (Reference channel)

- 6. i\_q\_filtered, I component (Reference channel)

- 7. i\_q\_filtered, Q component (Reference channel)

- 8. phase (Sample channel)

- 9. data (Sample channel)

- 10. data\_filtered (Sample channel)

- 11. i\_q, I component (Sample channel)

- 12. i\_q, Q component (Sample channel)

- 13. i\_q\_filtered, I component (Sample channel)

- 14. i\_q\_filtered, Q component (Sample channel)

Each of these has a corresponding bit in the channel\_enable and only if the bit is set the channel is sent to the dma\_wr interface, otherwise it is discarded. This allows an application to select which data channels it wants to capture.

## More Information

CN0363 HDL project

# CN0363 Phase Data Sync

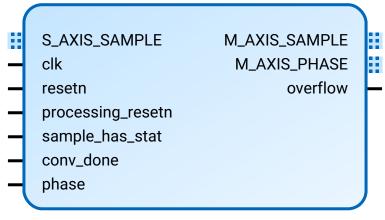

## cn0363\_phase\_data\_sync

The CN0363 Phase Data Sync FPGA Peripheral is part of the <u>EVAL-CN0363-PMDZ HDL reference design</u> and is responsible for preparing the ADC conversion result data and aligning it with the phase and feeding both to the processing pipeline.

## Files

| Name                                                                     | Description                                                                 |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| /library/cn0363/cn0363_phase_data_sync/<br>cn0363_phase_data_sync.v      | Verilog source for the peripheral.                                          |

| /library/cn0363/cn0363_phase_data_sync/<br>cn0363_phase_data_sync_ip.tcl | TCL script to generate the Vivado IP-integrator project for the peripheral. |

# Signal and Interface Pins

## S\_AXIS\_SAMPLE

AXI-Stream slave - Input sample data stream

| Physical Port                  | Logical Port | Direction | Dependency |

|--------------------------------|--------------|-----------|------------|

| <pre>s_axis_sample_valid</pre> | TVALID       | in        |            |

| <pre>s_axis_sample_ready</pre> | TREADY       | out       |            |

| <pre>s_axis_sample_data</pre>  | TDATA        | in [7:0]  |            |

## M\_AXIS\_SAMPLE

AXI-Stream master - Output sample data stream

| Physical Port | Logical Port | Direction | Dependency |

|---------------|--------------|-----------|------------|

|---------------|--------------|-----------|------------|

| Physical Port                  | Logical Port Direction |            | Dependency |

|--------------------------------|------------------------|------------|------------|

| <pre>m_axis_sample_valid</pre> | TVALID                 | out        |            |

| (m_axis_sample_ready)          | TREADY                 | in         |            |

| <pre>m_axis_sample_data</pre>  | TDATA                  | out [23:0] |            |

#### M\_AXIS\_PHASE

AXI-Stream master - Output phase data stream

| Physical Port                 | Logical Port | Direction  | Dependency |

|-------------------------------|--------------|------------|------------|

| (m_axis_phase_valid)          | TVALID       | out        |            |

| <pre>m_axis_phase_ready</pre> | TREADY       | in         |            |

| m_axis_phase_data             | TDATA        | out [31:0] |            |

#### Ports

| Physical Port              | Direction | Dependency | Description                                                                                                                                                              |

|----------------------------|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk                        | in        |            | Clock - All other signals are synchronous to this clock. Bus<br>S_AXIS_SAMPLE_M_AXIS_SAMPLE_M_AXIS_PHASE is<br>synchronous to this clock domain.                         |

| resetn                     | in        |            | Synchronous active low reset - Resets the internal state<br>machine of the core. Bus<br>S_AXIS_SAMPLE_M_AXIS_SAMPLE_M_AXIS_PHASE is<br>synchronous to this reset signal. |

| (processing_resetn)        | in        |            | Synchronous active low reset - Indicator that the processing pipeline is in reset.                                                                                       |

| <pre>sample_has_stat</pre> | in        |            | Input - Whether the incoming data on S_AXIS_SAMPLE has the STAT register appended.                                                                                       |

| conv_done                  | in        |            | Input - Conversion done signal from the ADC.                                                                                                                             |

| phase                      | in [31:0] |            | Input - Current excitation signal phase.                                                                                                                                 |

| overflow                   | out       |            | Input - The overflow signal is asserted if a new sample arrives before the previous one has been consumed.                                                               |

# Theory of Operation

The CN0363 Phase Data Sync FPGA Peripheral takes the raw ADC sample data read by a SPI controller from the ADC on the S\_AXIS\_SAMPLE stream. The data is assembled into 24-bit word and converted from offset binary to two's complement signed.

When a rising edge is detected on the conv\_done signal the core takes a snapshot of the phase input signal. This data will be assumed to the phase that belongs to the next incoming data sample on the S\_AXIS\_SAMPLE. The data is aligned with the corresponding phase data and both are send out on the  $M_{AXIS}SAMPLE$  and  $M_{AXIS}PHASE$  stream.

If the sample\_has\_stat signal is asserted the core will receive 32-bit instead of 24-bit per sample on the S\_AXIS\_SAMPLE stream. The last 8-bit are assumed to contain the STAT register of the ADC, which among other things contains the information about which channel the ADC result belongs to. This information can be used to detect and fix channel swaps. If sample\_has\_stat is not asserted the core assumes that no channel swaps happen and the whole pipeline is always running fast enough to accept a sample before the next one is ready.

If processing\_resetn is asserted the processing pipeline is assumed to be in reset and incapable of accepting new samples and when a new sample arrives at the (S\_AXIS\_SAMPLE) port a overflow condition is generated. The signal also resets the channel swap detection logic and makes sure that the next sample that is inserted into the processing pipeline after the reset belongs to the first channel.

# More Information

CN0363 HDL project