# Analog<sup>®</sup>And Telecommunication Electronics – Mini-Project

Politecnico Di Torino 06/06/2016

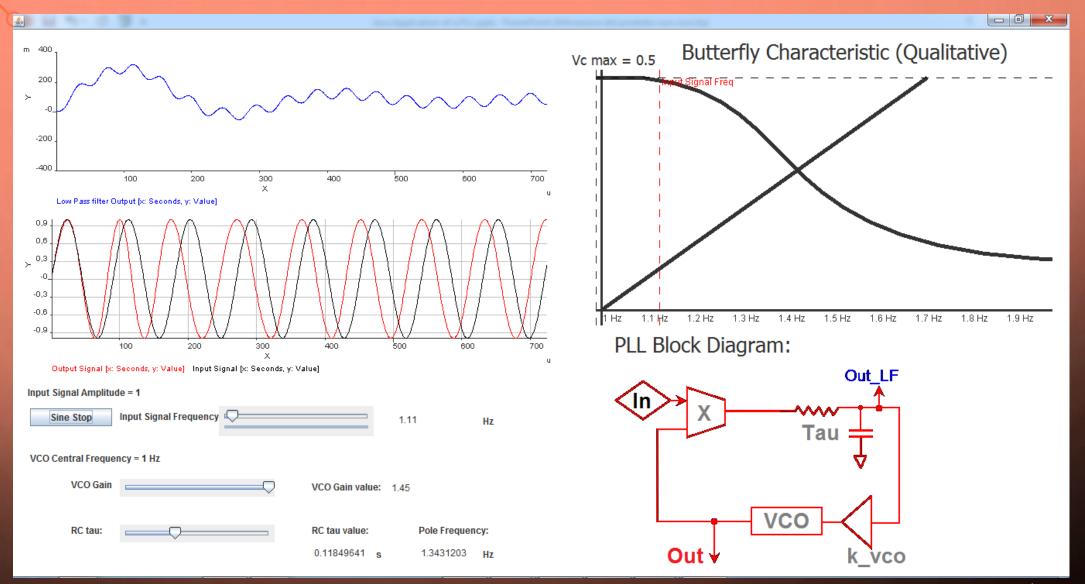

#### JAVA APPLICATION OF A PHASE LOCK LOOP

Authors: Jurgen Kello Luigi Zaffarana

ABSTRACT:

PHASE-LOCK LOOPS ARE USUALLY IMPLEMENTED TO EVALUATE THE FREQUENCY OF A SINUSOID IN THE PRESENCE OF NOISE AND TO TRACK THE FREQUENCY OF THIS SIGNAL AS IT CHANGES. THIS DOCUMENT DESCRIBES THE DEVELOPMENT OF A JAVA SOFTWARE TO EMULATE THE BEHAVIOUR OF A PHASE-LOCK LOOP.

## OUTLINE:

- Overview of the Phase-Locked Loop

- Software realization of each block

- Graphical Interface

- DEMO

#### **OVERVIEW OF THE PHASE-LOCKED LOOP**

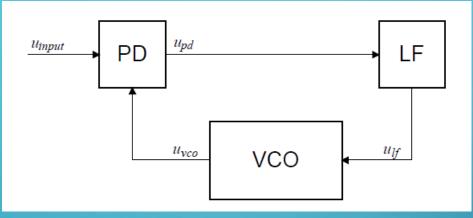

The three basic components of a standard PLL are:

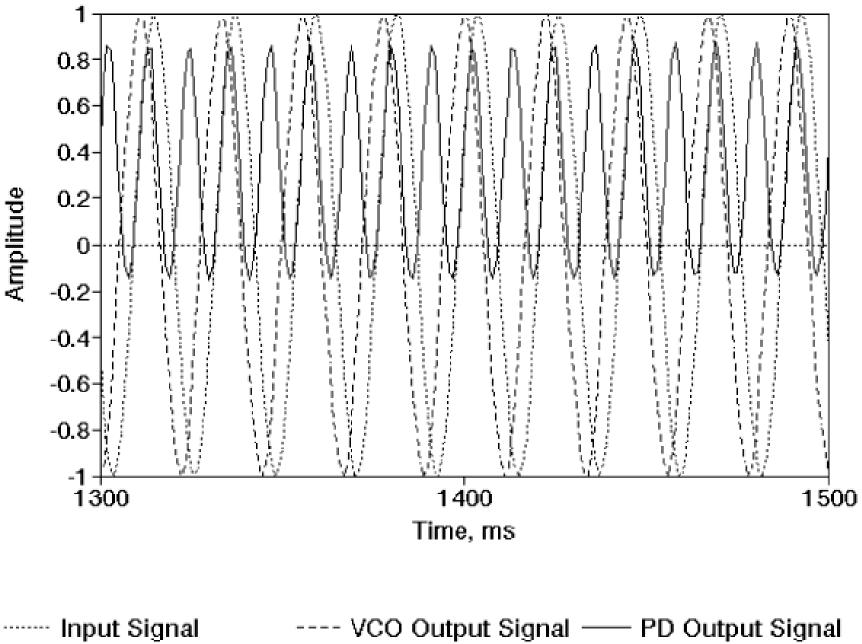

As a phase detector a simple multiplier can be used, which multiplies the input with the output of the voltage controlled oscillator and the result will be the sum of a DC with a time varying component.

The sum beat on the other hand will be cut off by the loop filter. The mean value of the filter output will determine the operating frequency of the VCO

So due to this feedback loop it is possible to have the output of the VCO with the same frequency as the input and with approximately 90 degree of phase shift.

## PHASE DETECTOR

A simple analog phase detector will be just a multiplier :

$u_{input}(t) = A\sin(\omega t + \theta_1)$

$u_{vco}(t) = B \sin(\omega t + \theta_2)$

The output of the phase detector will be:

$u_{pd}(t) = K_d \frac{AB}{2} \left[ \cos(\theta_1 - \theta_2) + \cos(2\omega t + \theta_1 + \theta_2) \right] \quad K_d \to Phase \ detector \ Gain$

So the DC component mentioned before depends on the sine of the phase difference between input and VCO output.

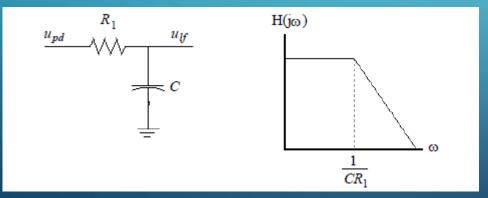

## LOOP FILTER

The AC components of the phase detector output are attenuated by this filter.

BW = -

Having a small bandwidth, meaning cutting off most of the AC components, would result in having a large time constant, which means to have a slow response, then a slow response may reduce the ability of the PLL to remain locked.

The transfer function for the filter will be given by:

$$H(j\omega) = \frac{1}{j\omega CR_1 + 1}$$

#### VCO

The output signal frequency of the VCO is linearly dependent on an input signal For this application, the VCO signal at the output is given by the following expression:  $u_{vco}(t) = \sin((K_0 \ lpf_{out}(t) + \omega_{or})t) \ where:$  $-lpf_{out}(t)$  is the loop Filter Output  $-K_0$  is the gain of the VCO

$-\omega_{or}$  is the Centre Frequency of the VCO

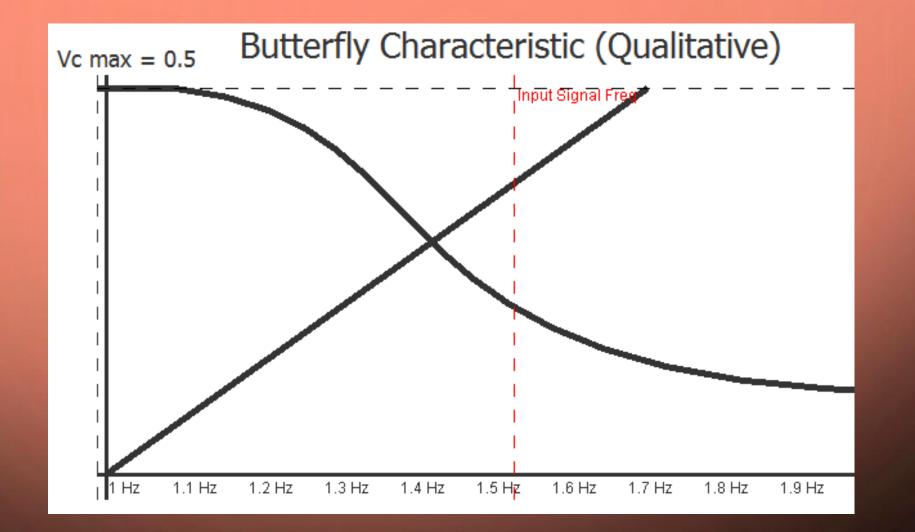

## **BUTTERFLY CHARACTERISTIC**

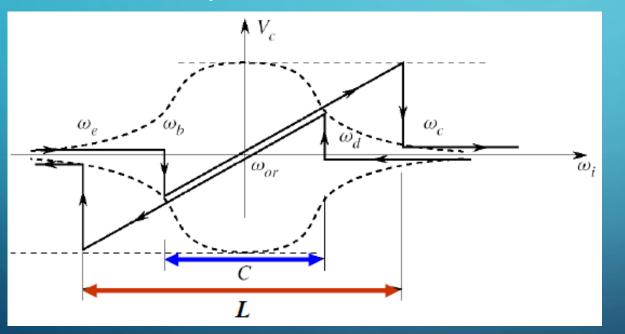

As we know from theory, to determine the behaviour of the PLL, is possible to use the Butterfly Characteristic :

In our Software realization we will just use the first quadrant

Assuming 2 signals with amplitude of 1V the  $V_c$  maximum value at the output will be of 0.5V.

## **SOFTWARE REALIZATION OF EACH BLOCK**

## THE PHASE DETECTOR

As described before, an analog phase detector for a PLL will consist of a multiplication of the input signal with the VCO output signal.

phase\_detector = k\_phd \* u\_out \* u\_in;

## THE LOOP FILTER

To realize a software version of the Filter, transform in the z-Domain should be applied to arrive at the Digital version of it.

For this implementation of the software, we preferred to not use a system described in the z-domain since that would imply to use vectors, which would increase the computational cost of the system

s\_delu\_dt = s\_delu\_dt + (phase\_detector - lpf\_out) \* (dt\_r);

lpf\_out = (float) ((float) s\_delu\_dt / (cr));

(see reference [3] for more details)

### **VOLTAGE CONTROLLED OSCILLATOR**

A discrete-time software implementation of the VCO was developed by incrementing a phase angle  $\theta(t)$  using a circle with unitary radius (because the input signal will always have a unitary amplitude).

$\theta(t) = \theta(t-1) + (\omega_0 + u_{lf(t)}) T_S$

$u_{vco}(t) = \sin(\theta(t))$

The software realization of these relations will be straightforward: phase u out = phase u out + ((float)(2\*dt r\*Math.PI) \*(f0 +(k vco\*lpf out)));

u\_out = (float) ((float)A \* Math.sin( phase\_u\_out ));

#### Input Signal Amplitude = 1

14/15

$\bigcirc$

$\bigcirc$

#### **REFERENCES:**

- D. Del Corso: Elettronica per Telecomunicazioni McGraw Hill, Settembre 2002 [Cap3]

- 2. "The Automated Software phase locked loop and the exploration of ad adaptive algorithm for the adjustment of PLL Parameters" by Kevin Rolfes thesis [Theory about realization of the Software PLL and Images related to results] Source:<u>www.rolfes.org/kevin rolfes msee thesis.pdf</u>

- **3.** Roland E. Best: Phase-Locked Loops Theory, Design, and Applications McGraw-Hill, 1993, ISBN 0-07-911386-9 [PLL Parameters and Theory related to PLL]

16