# Effective Power/Ground Plane Decoupling for PCB

Dr. Bruce Archambeault

IBM Distinguished Engineer

IEEE Fellow

IBM

Research Triangle Park, NC

Barch@us.ibm.com

October 2007

### Power Plane Noise Control

#### Power/Ground-Reference Plane Noise

- Must consider TWO Major Factors

- EMC -- Reduce noise along edge of board from IC somewhere else

- Functionality -- Provide IC with sufficient charge

- Decoupling strategies are FULL of <u>Myths</u>

- Consider the physics

- Don't forget <u>Inductance!</u>

## Source of Power/Ground-Reference Plane Noise

- Power requirements from IC during switching

- Critical Net currents routed through via

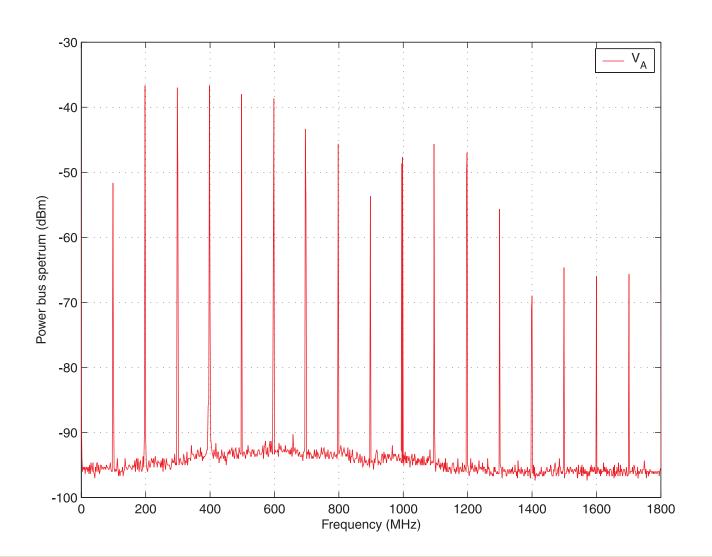

# Power Bus Spectrum Clock Driver IDT74FCT807

## Noise Injected between Planes Due to Critical Net Through Via

FR4  $\varepsilon_r$ =4.2 Loss tan=0.02

### Transfer Function from Via to I/O Pin

# Decoupling Must be Analyzed in Different Ways for Different Functions

#### • EMC

- Resonance big concern

- Requires STEADY-STATE analysis

- Frequency Domain

- Transfer function analysis

- Eliminate noise along edge of board due to ASIC/IC located far away

# Decoupling Must be Analyzed in Different Ways for Different Functions

- Provide Charge to ASIC/IC

- Requires TRANSIENT analysis

- Charge will NOT travel from far corners of the board fast enough

- Local decoupling capacitors dominate

- Impedance at ASIC/IC pins important

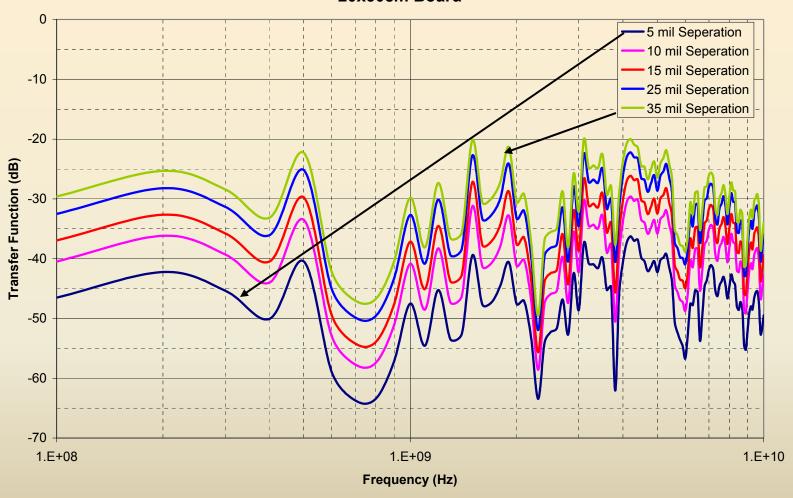

## Steady-State Analysis

- Measurements and Simulations

- Test Board with Decoupling capacitors every 1" square

### **Test Board Ports**

October 2007

Dr. Bruce Archambeault

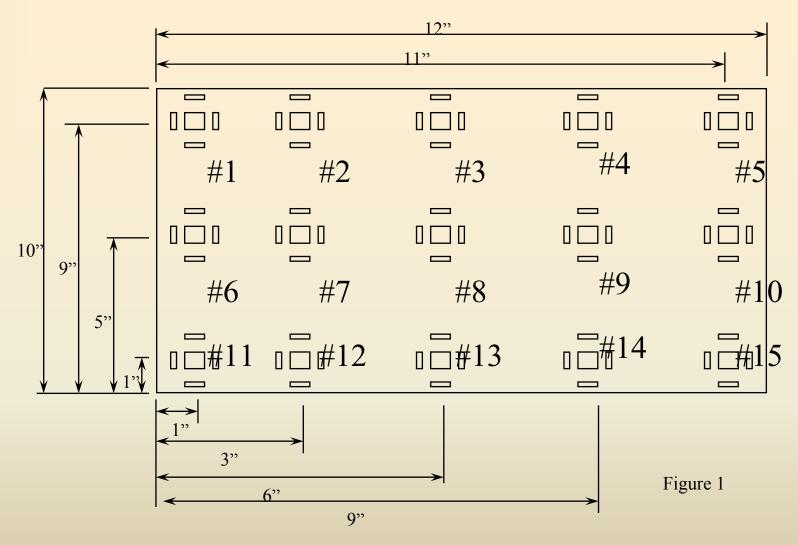

## S21 Used for Decoupling "Goodness"

- Ratio of Power 'out' to power 'in'

- Better Indicator of EMI noise transmission across board

- Also used to validate simulations

## Measured S21 for 12" x 10" PC Board Between Power/Ground Planes with No Decoupling Capacitors (Measured Center to Corner)

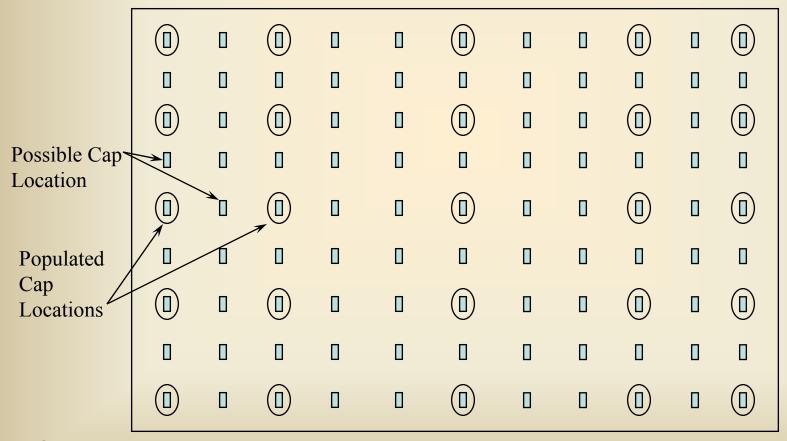

# Test Board Decoupling Capacitor Placement for 25.01 uf Caps

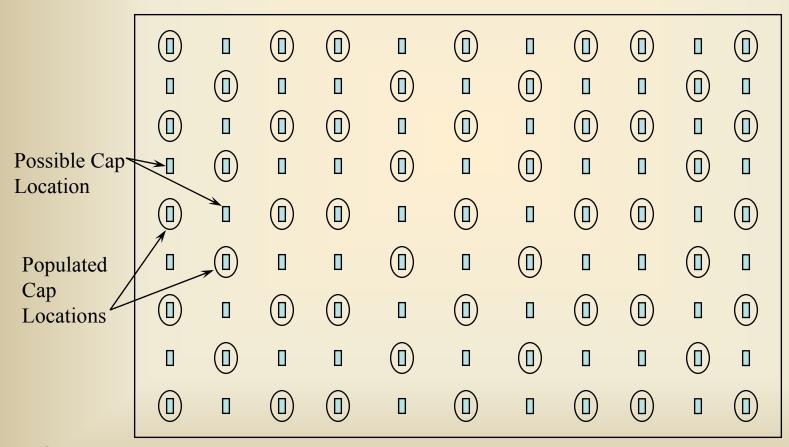

# Test Board Decoupling Capacitor Placement for 51.01 uf Caps

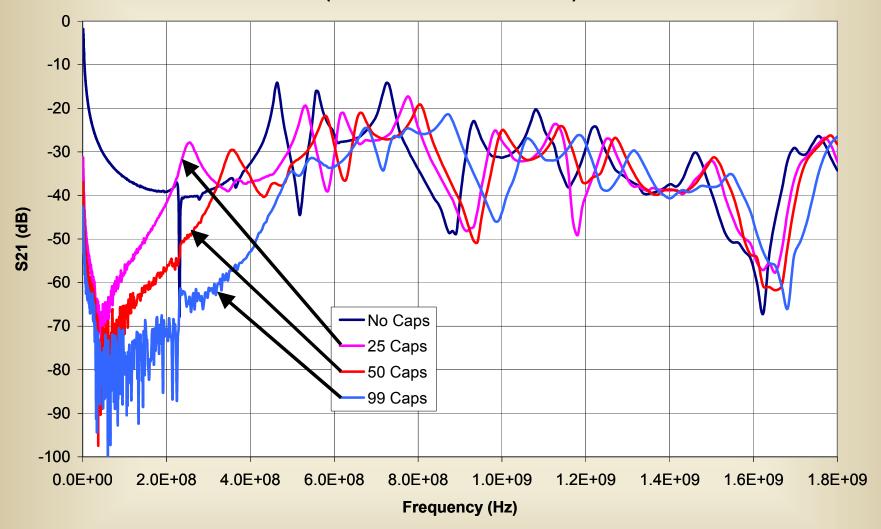

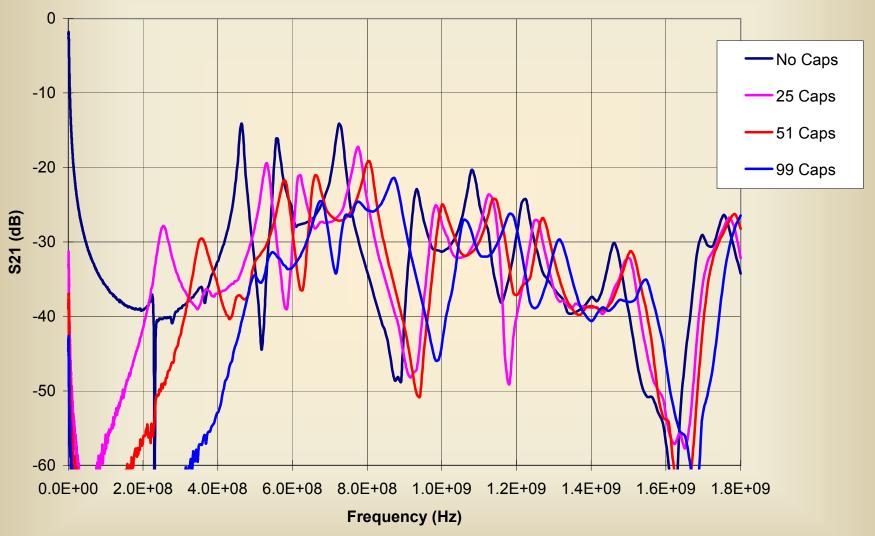

## Measured S21 for 12" x 10" PC Board Between Power/Ground Planes with Various Amounts of Decoupling Capacitors (Measured Center to Corner)

## S21 Between Port #8 and Port #1 on Test Board With Various Amounts of .01 uf Decoupling Capacitors

Dr. Bruce Archambeault

17

October 2007

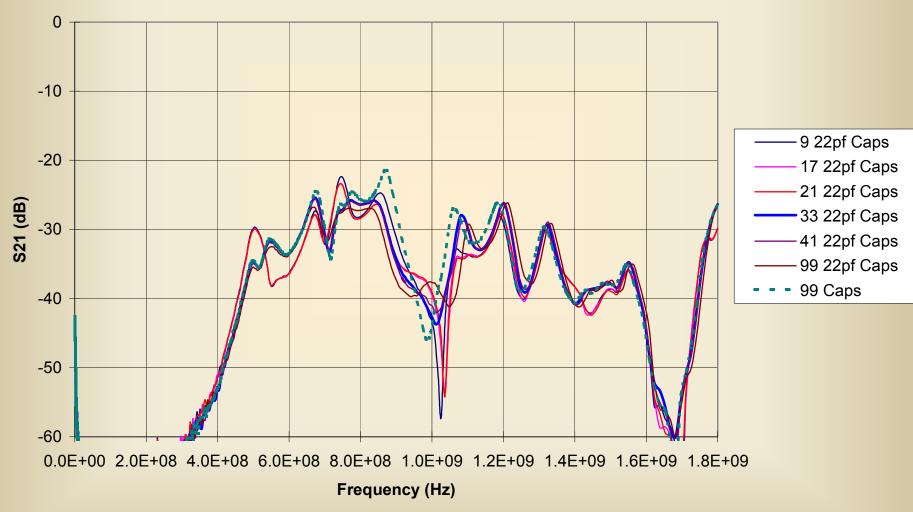

### Test Board Decoupling Capacitor Placement for 41 22pf Caps (In Addition to 99 .01uf Caps)

## S21 Between Port #8 and Port #1 on Test Board With 99 .01 uf Decoupling Capacitors and Various Amounts of 22pf Capacitors Added

October 2007

Dr. Bruce Archambeault

20

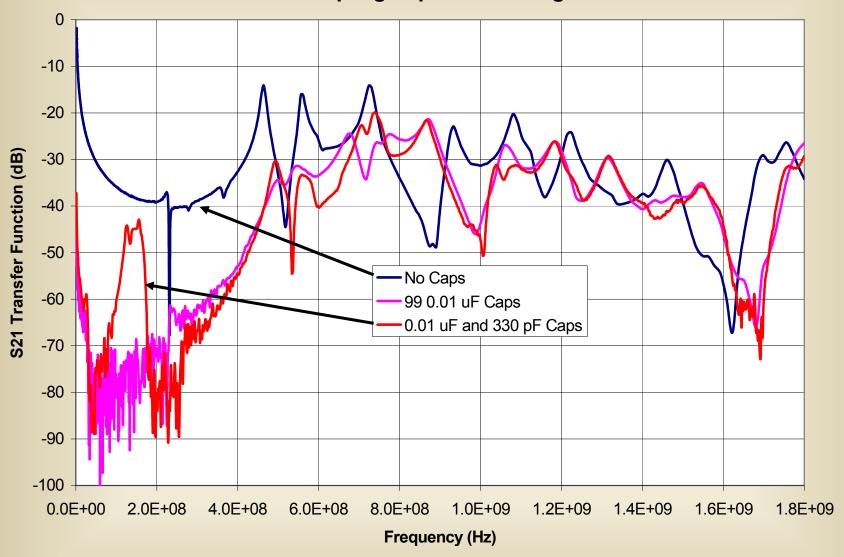

#### Measured Comparison of Multiple and Single Value Decoupling Capacitor Strategies

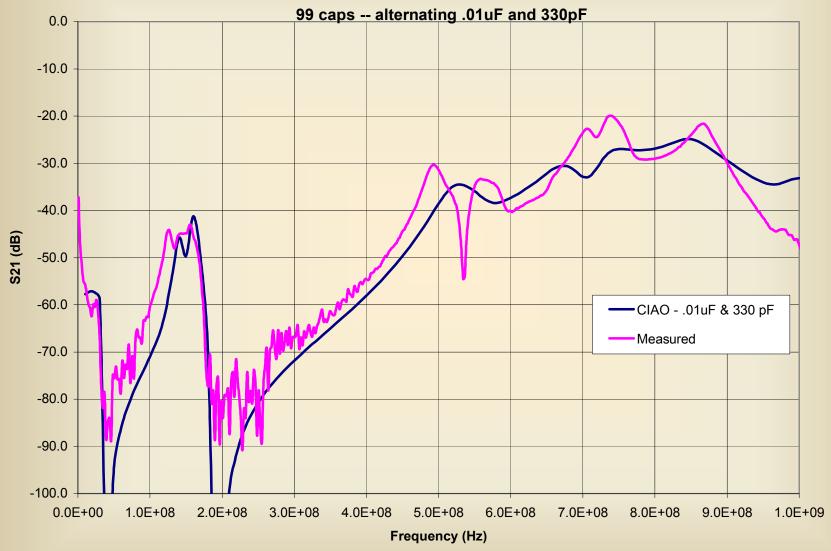

#### Comparison of Model and Measured Data for 10" x 12" Board

Dr. Bruce Archambeault

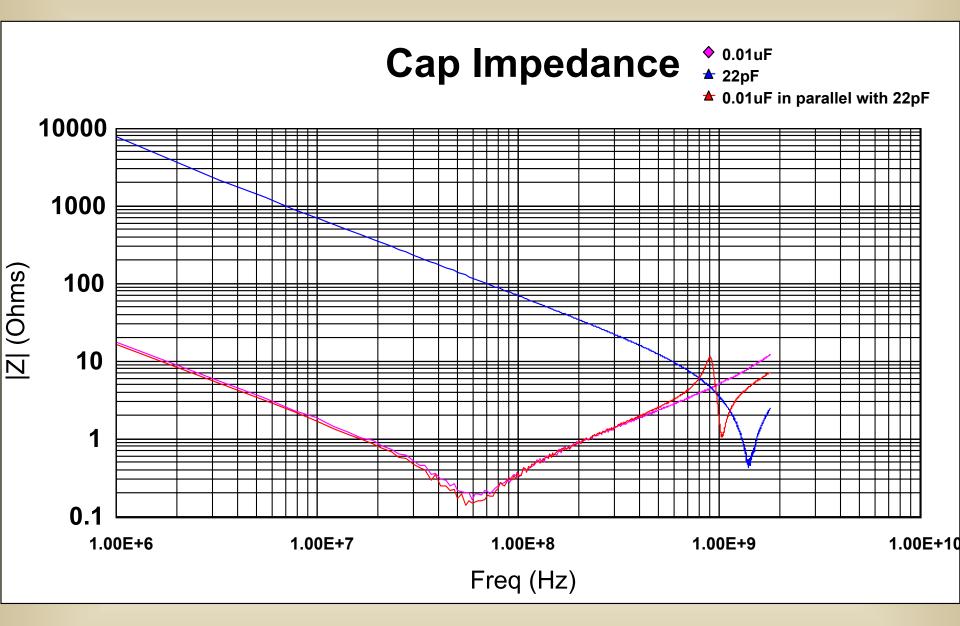

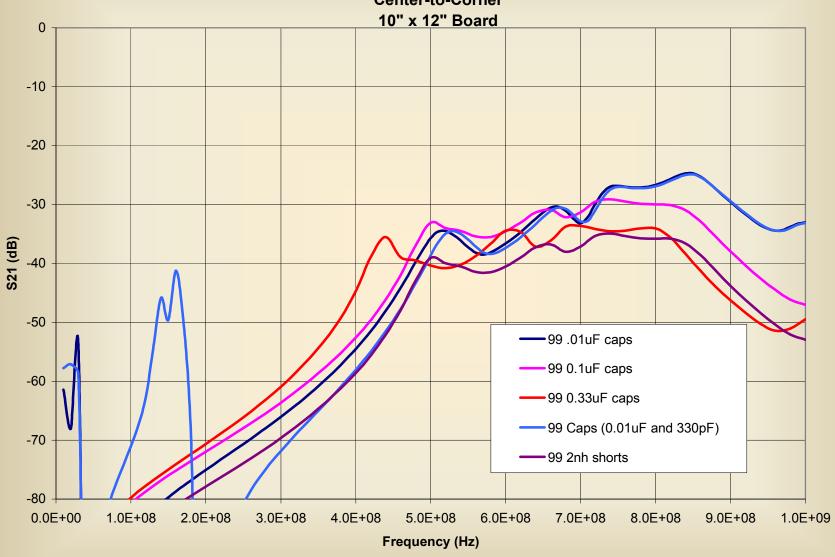

#### S21 Transfer Function for Different Value Capacitors Center-to-Corner

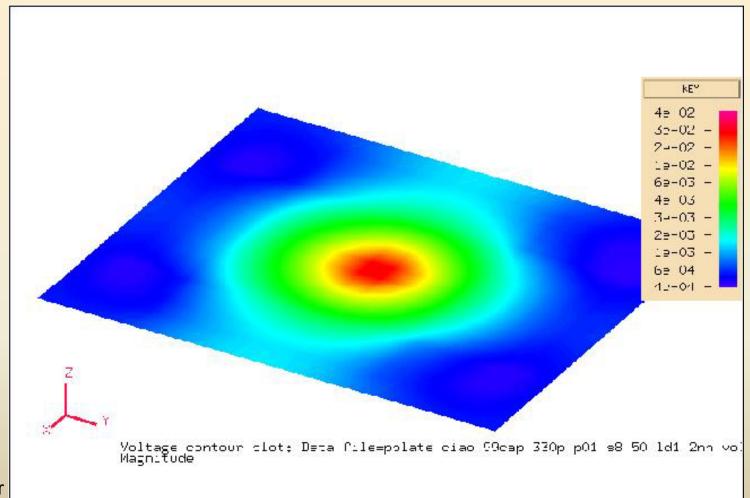

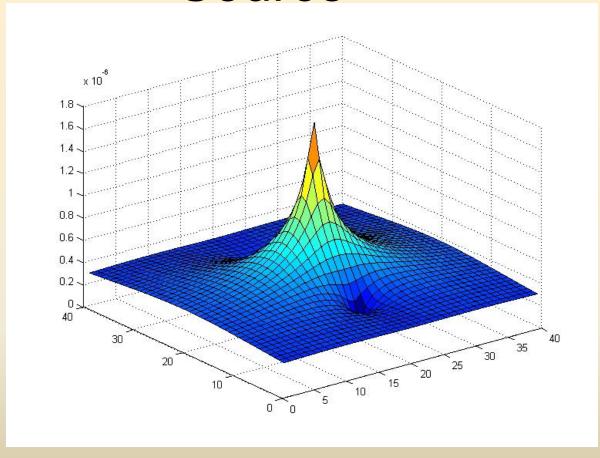

# Voltage Distribution @ 350 MHz .01uF and 330pF Case (Source in Center)

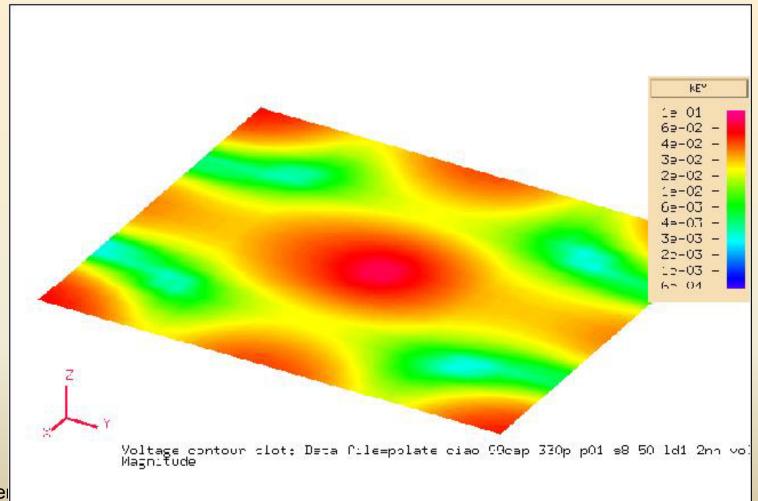

# Voltage Distribution @ 750 MHz .01uF and 330pF Case (Source in Center)

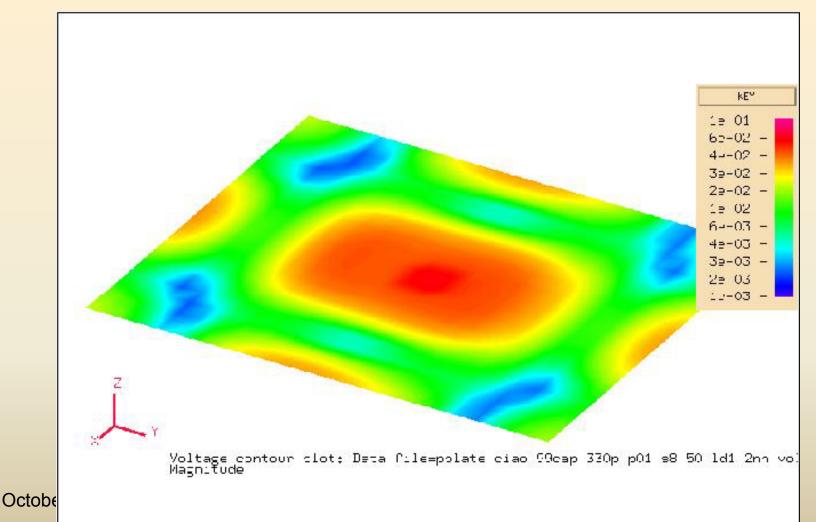

# Voltage Distribution @ 950 MHz .01uF and 330pF Case (Source in Center)

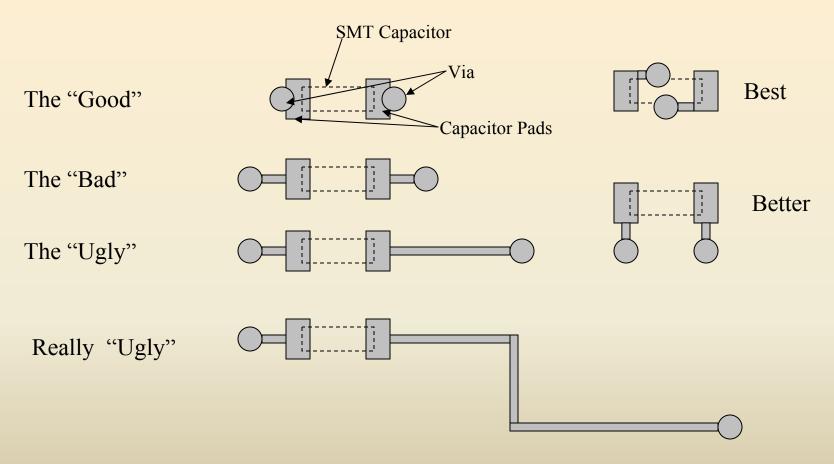

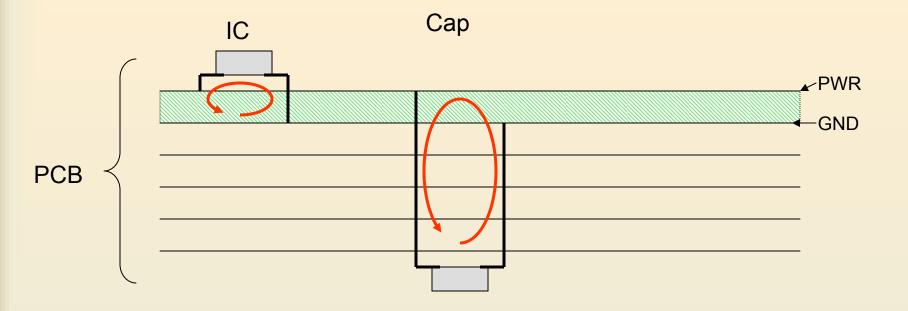

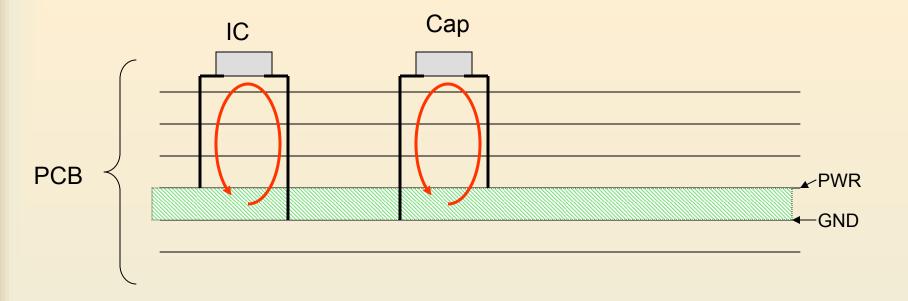

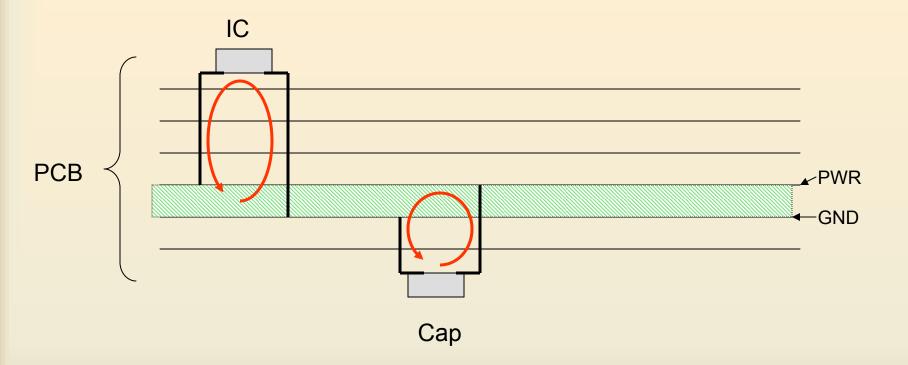

## **Decoupling Capacitor Mounting**

Keep as to planes as close to capacitor pads as possible

## Decoupling Capacitor Mounting

Keep as to planes as close to capacitor pads as possible

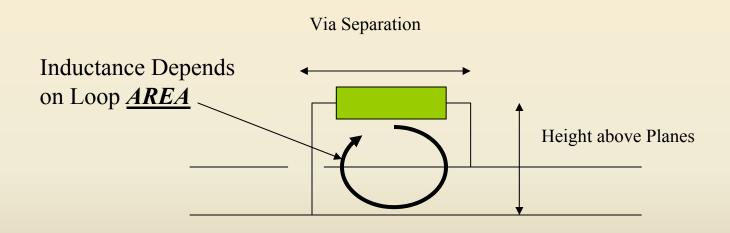

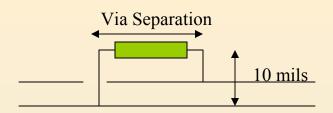

# Via Configuration Can Change Inductance

#### Comparison of Decoupling Capacitor Impedance 100 mil Between Vias & 10 mil to Planes

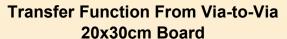

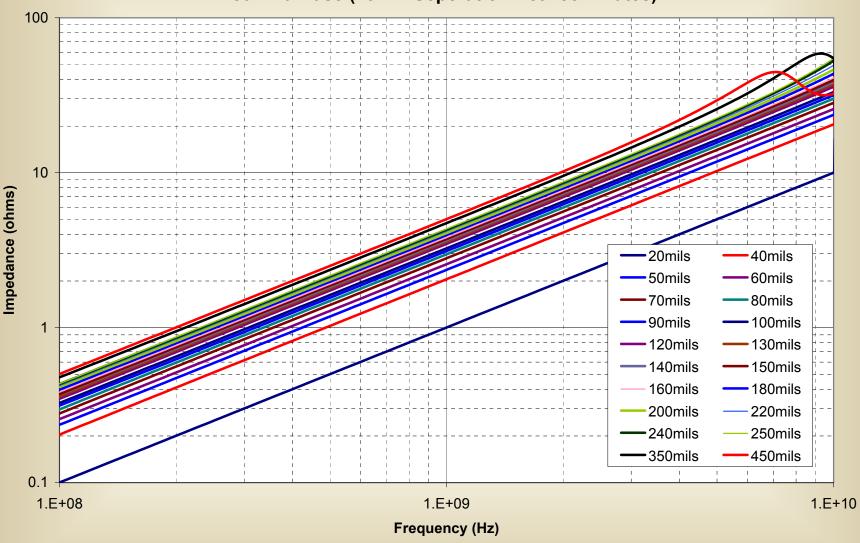

# Comparison of Decoupling Capacitor Via Separation Distance Effects

0.1 uF Capacitor

| Via Seperation (mils) | Inductance (nH) | Impedance @ 1 GHz (ohms) |

|-----------------------|-----------------|--------------------------|

| 20                    | .06             | .41                      |

| 40                    | 0.21            | 1.3                      |

| 60                    | 0.36            | 2.33                     |

| 80                    | 0.5             | 3.1                      |

| 100                   | 0.64            | 4.0                      |

| 150                   | 1.0             | 6.23                     |

| 200                   | 1.4             | 8.5                      |

| 300                   | 2.1             | 12.69                    |

| 400                   | 2.75            | 17.3                     |

| 500                   | 3.5             | 21.7                     |

### **Example Connection Inductance Values**

| Spacing<br>between<br>Vias | Complex<br>Formula<br>(20 mils to<br>plane) | Simple rect loop<br>(20 mils to<br>plane) | Complex Formula<br>(10 mils to plane) | Simple rect loop<br>(10 mils to plane) |

|----------------------------|---------------------------------------------|-------------------------------------------|---------------------------------------|----------------------------------------|

| 0805 + 2*10mil             | 3.0 nH                                      | 3.1 nH                                    | 2 nH                                  | 1.38 nH                                |

| 0805 +<br>2*100mil         | 4.1 nH                                      | 4.3 nH                                    | 3 nH                                  | 2.0 nH                                 |

| 0805 +<br>2*160mil         | 5.1 nH                                      | 5.1 nH                                    | 3.5 nH                                | 2.5 nH                                 |

| 0603 + 2*10mil             | 2.3 nH                                      | 1.74 nH                                   | 1.1 nH                                | 0.8 nH                                 |

| 0603 +<br>2*100mil         | 3.3 nH                                      | 3.15 nH                                   | 2.1 nH                                | 1.5 nH                                 |

| 0603 +<br>2*160mil         | 4.2 nH                                      | 4.3 nH                                    | 2.4 nH                                | 2.07 nH                                |

Sources for complex formula:

Knighten, James L., Bruce Archambeault, Jun Fan, Samuel Connor, James L. Drewniak, "PDN Design Strategies: II. Ceramic SMT Decoupling Capacitors – Does Location Matter?," *IEEE EMC Society Newsletter*, Issue No. x, Winter 2006, pp. 56-67. (www.emcs.org)

Fan, Jun, Wei Cui, James L. Drewniak, Thomas Van Doren, and James L. Knighten, "Estimating the Noise Mitigating Effect of Local Decoupling in Printed Circuit Boards," *IEEE Trans. on Advanced Packaging*, Vol. 25, No. 2, May 2002, pp. 154-165.

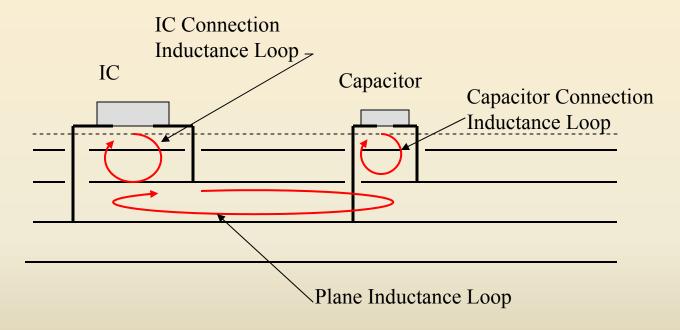

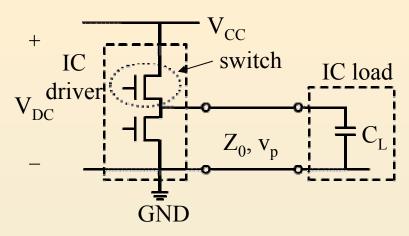

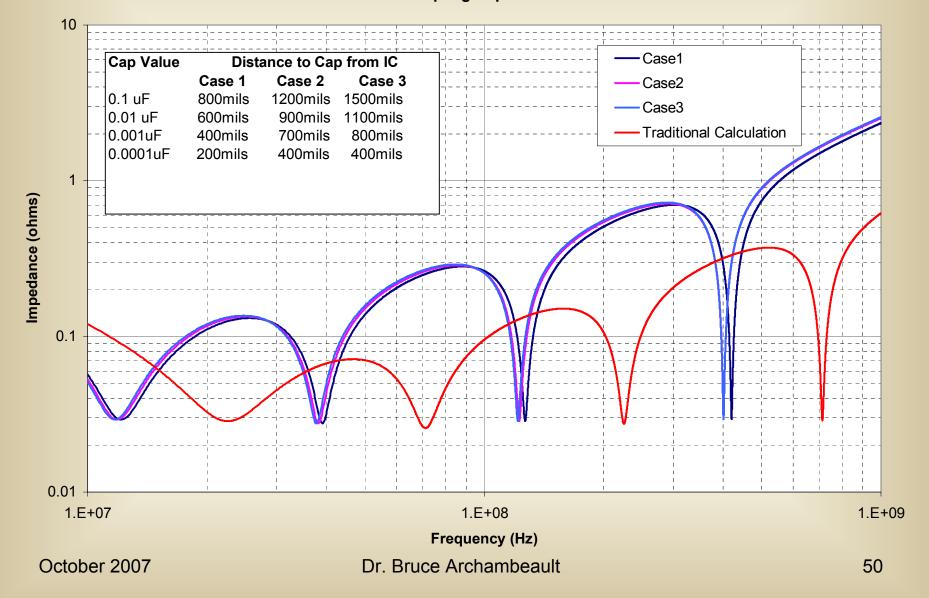

# Transient Analysis (Time Limited)

- Provide charge to ASIC/IC

- Inductance dominates impedance

- Loop area 1<sup>st</sup> order effect

- Traditional analysis not accurate enough

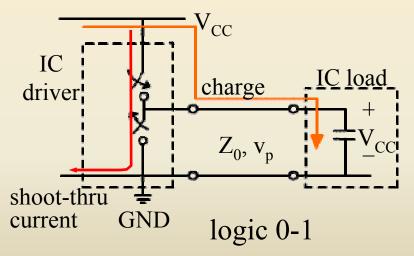

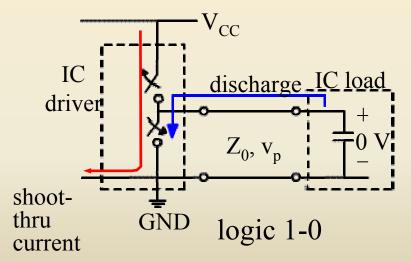

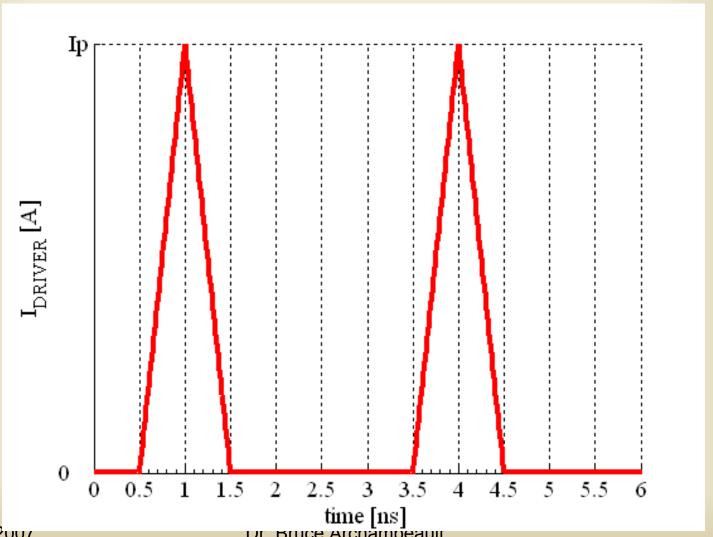

## Current in IC During Logic Transitions (CMOS)

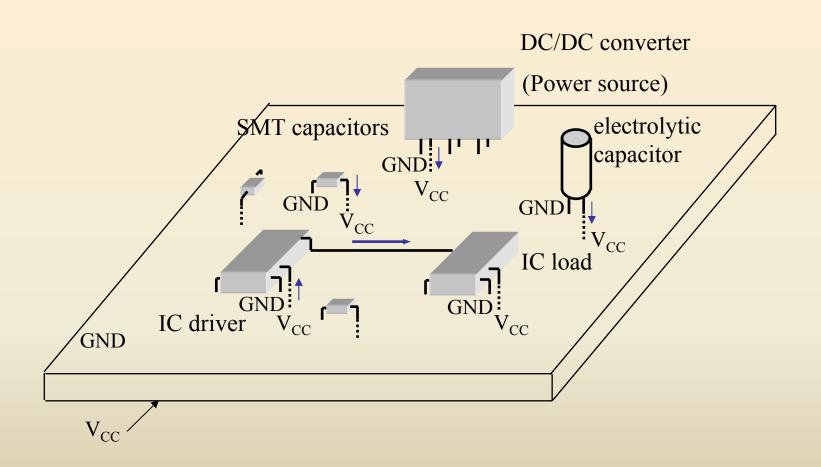

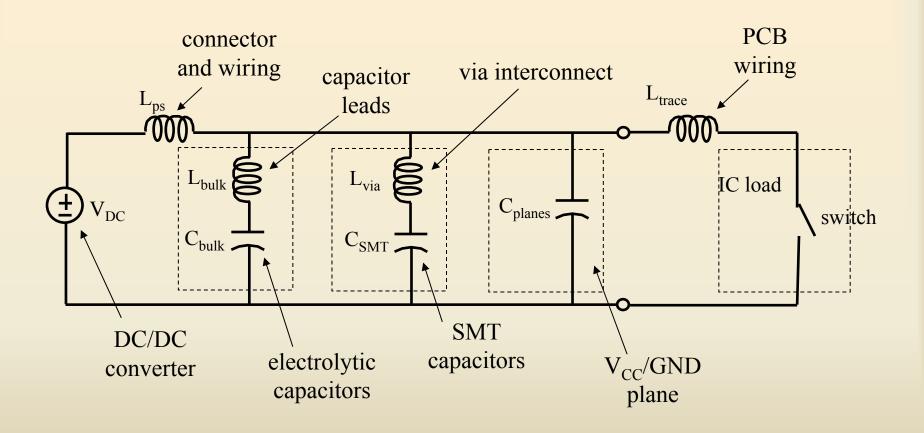

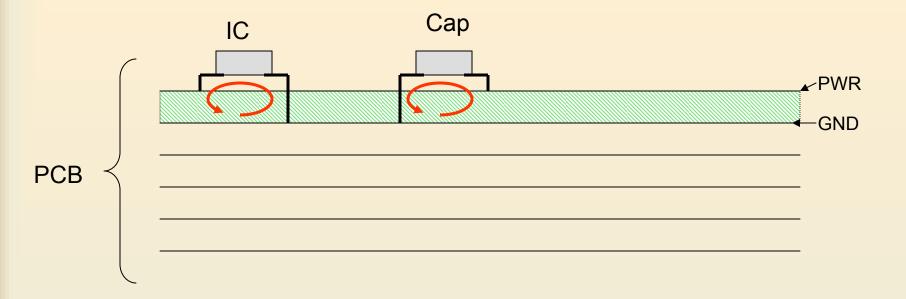

## Typical PCB Power Delivery

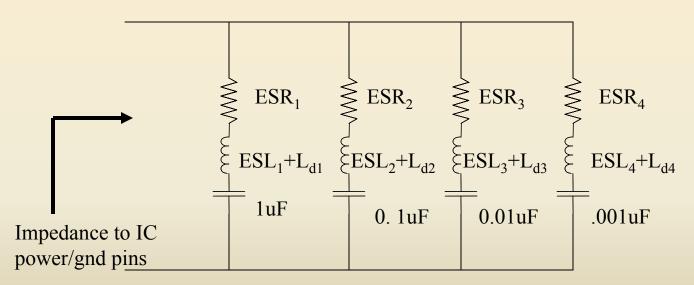

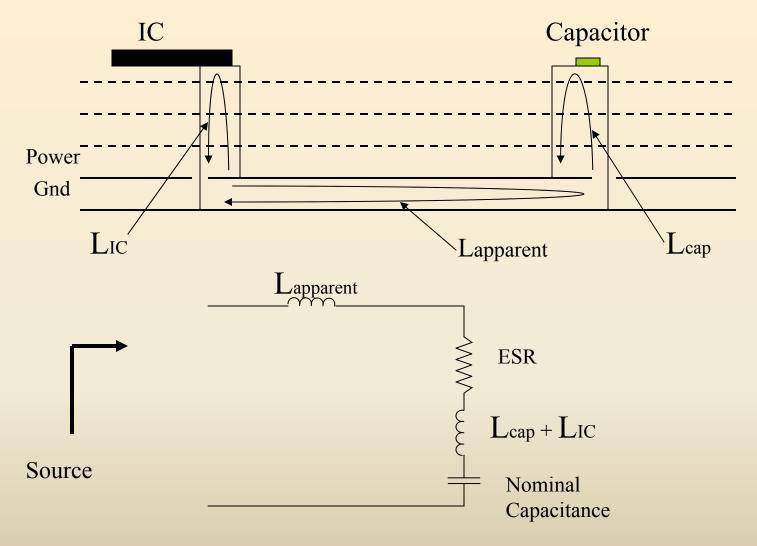

# Equivalent Circuit for Power Current Delivery to IC

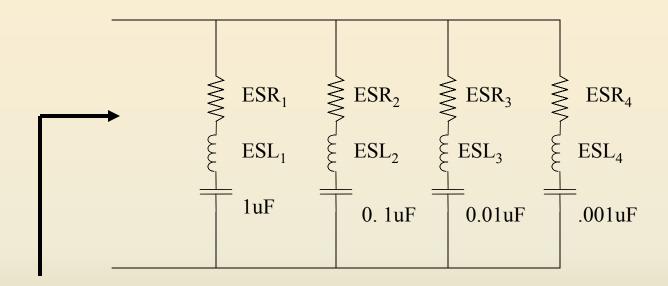

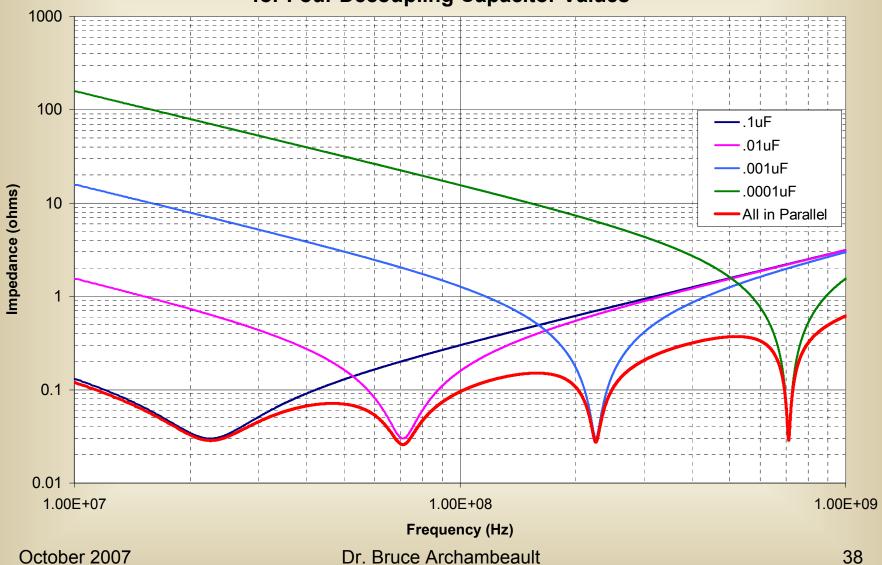

## **Traditional Analysis #1**

Use impedance of capacitors in parallel

Impedance to IC power/gnd pins

No Effect of Distance Between Capacitors and IC Included!

## Traditional Analysis #2

- Calculate loop area Traditional loop Inductance formulas

- Which loop area? Which size conductor

Over Estimates L and Ignores Distributed Capacitance

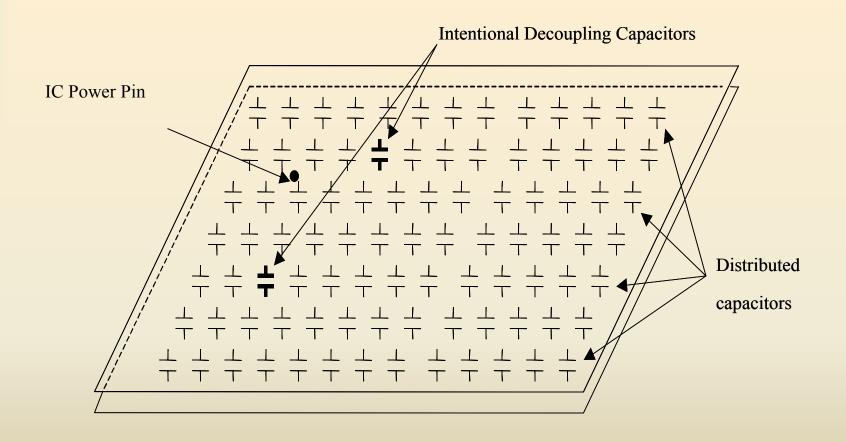

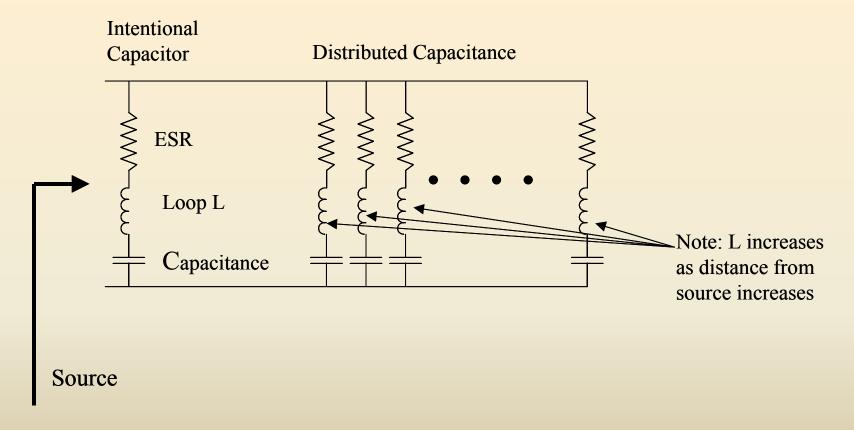

## More Accurate Model Includes Distributed Capacitance

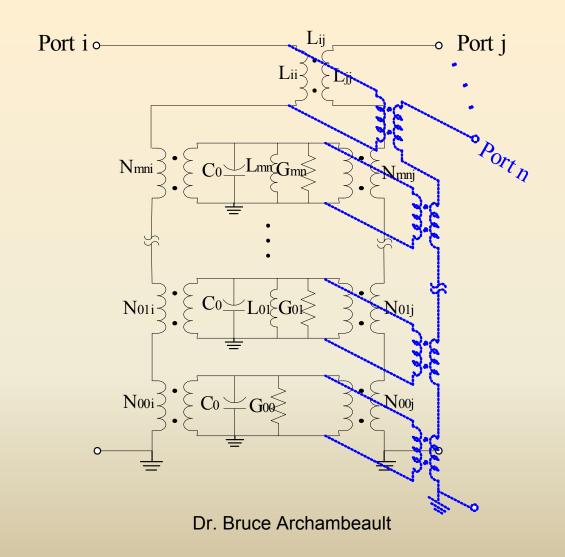

## Distributed Capacitance Schematic

## Effect of Distributed Capacitance

- Can NOT be calculated/estimated using traditional capacitance equation

- Displacement current amplitude changes with position and distance from the source

# Displacement Current 500 MHz via @450 mils from Source

## Need to Find the Real Effect of Decoupling Capacitor Distance

- Perfect decoupling capacitor is a via between planes

- FDTD simulation to find the effect of shorting via distance from source

- Vary spacing between planes, distance to via, frequency, etc

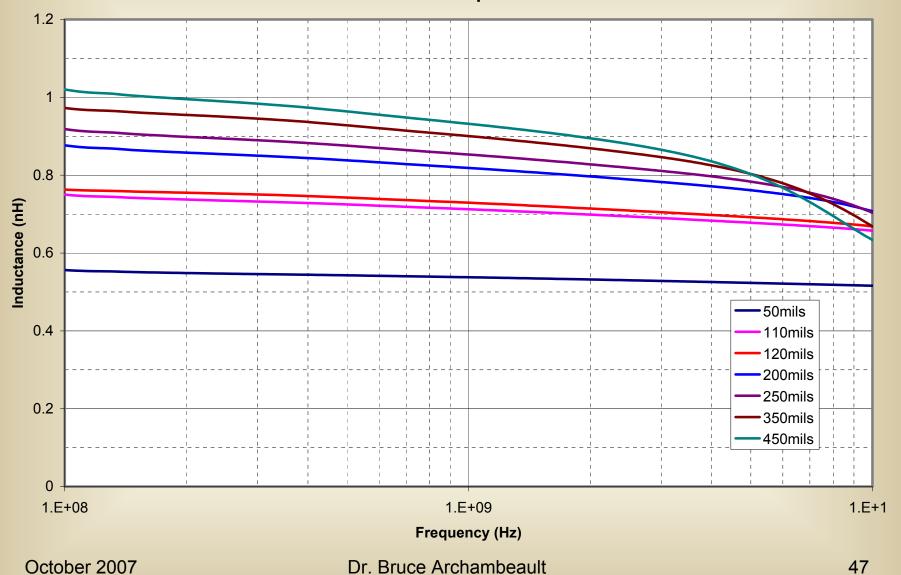

### Impedance of Shorting Via vs. Frequency Four Via Case (20 mil Seperation Between Plates)

## Impedance Result

- Linear with frequency (on log scale)

- Looks like an inductance only!

- Consider this inductance an Apparent Inductance

- Apparent inductance is constant with frequency

## Apparent Inductance for One Shorting Via Case 20 mil Plate Separation

## Formulas to Predict Apparent Inductance

$$\begin{split} L_{one-via} &= (0.1336s - 0.0654) Ln(dist) + (-0.2609s + 0.2675) \\ L_{two-via} &= (0.1307s - 0.0492) Ln(dist) + (-0.2948s + 0.1943) \\ L_{three-via} &= (0.1242s - 0.0447) Ln(dist) + (-0.2848s + 0.1763) \\ L_{four-via} &= (0.1192s - 0.0403) Ln(dist) + (-0.2774s + 0.1592) \end{split}$$

s = separation between plates (mils/10)

dist = distance to via

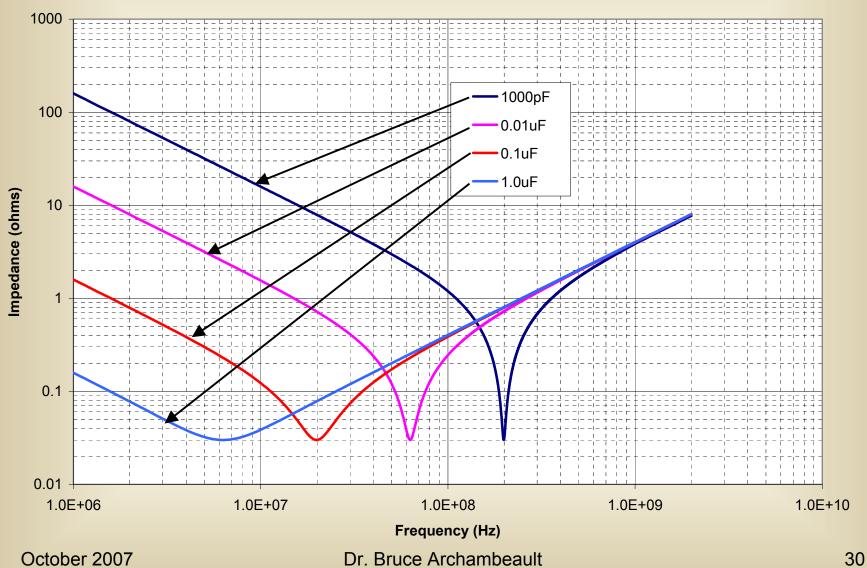

#### True Impedance for Decoupling Capacitor

#### Impedance Calculation with Apparent Inductance for Four Decoupling Capacitor Values

## Effect of Distributed Capacitance

- Can NOT be calculated/estimated using traditional capacitance equation

- Displacement current amplitude changes with position and distance from the source

- Following examples use cavity resonance technique (EZ-PowerPlane)

- Frequency Domain to compare to measurements

- Time Domain using SPICE circuit from cavity resonance analysis

## Parameters for Comparison to Measurements

- Dielectric thickness = 35 mils

- Dielectric constant = 4.5, Loss tan = 0.02

- Copper conductivity = 5.8 e7 S/m

#### Measured vs Model (MoM) S21 for 12" x 10" PC Power/gnd with 25 .01uF caps

Dr. Bruce Archambeault

53

October 2007

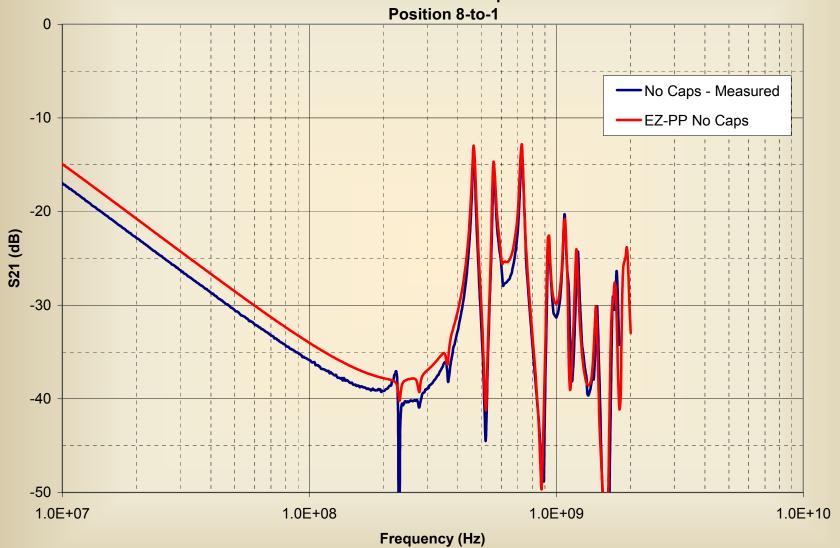

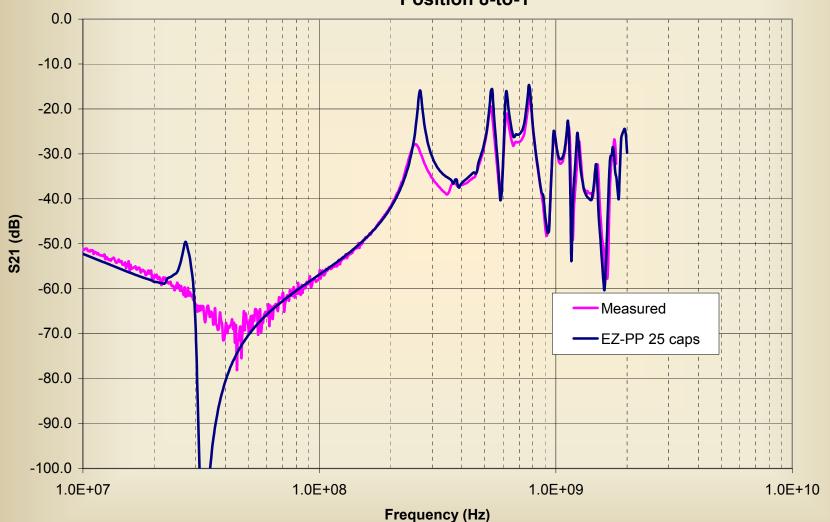

## Measured vs Model (EZ-PP) S21 for 12" x 10" PC Power/gnd with 25 .01uF caps Position 8-to-1

October 2007

Dr. Bruce Archambeault

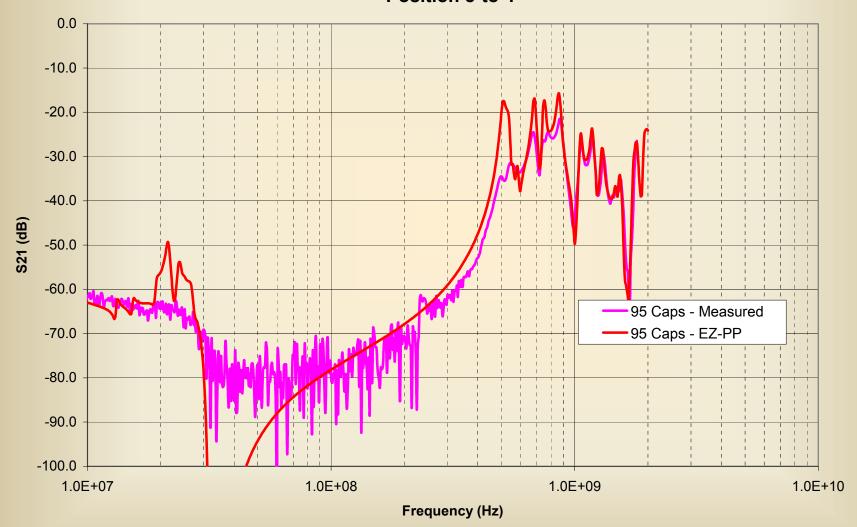

## Measured vs Model (EZ-PP) S21 for 12" x 10" PC Power/gnd with 95 .01uF caps Position 8-to-1

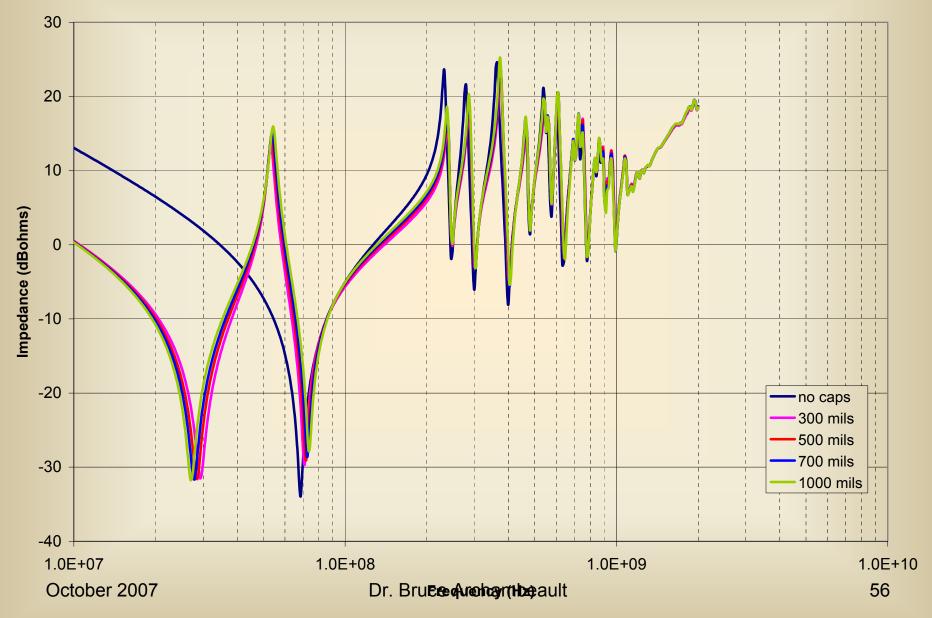

Impedance at Port #1

Single 0.01 uF Capacitor at Various Distances (35mil Dielectric)

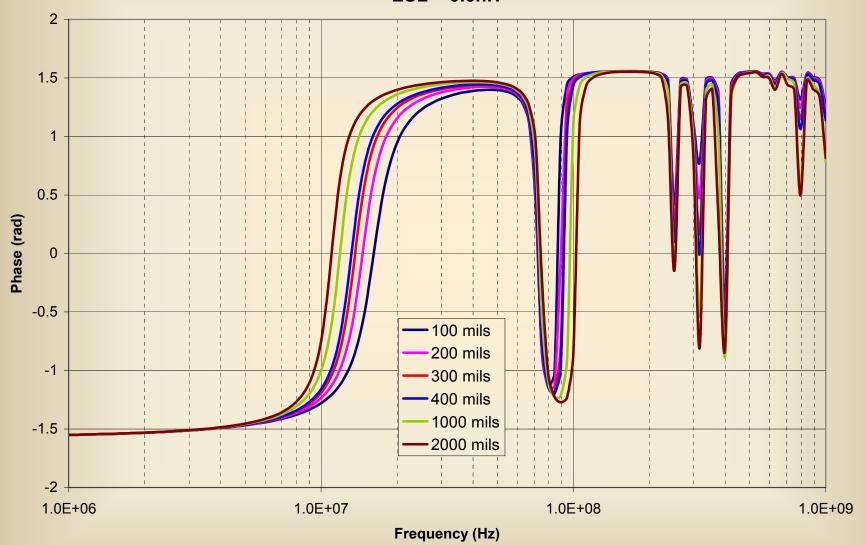

Z11 Phase Comparison as Capacitor distance Varies for 35 mils FR4 ESL = 0.5nH

October 2007 Dr. Bruce Archambeault

Impedance at Port #1

Single 0.01 uF Capacitor at Various Distances (10mil Dielectric)

## Cavity Resonance (EZ-PowerPlane) Equivalent Circuit for HSPICE

October 2007

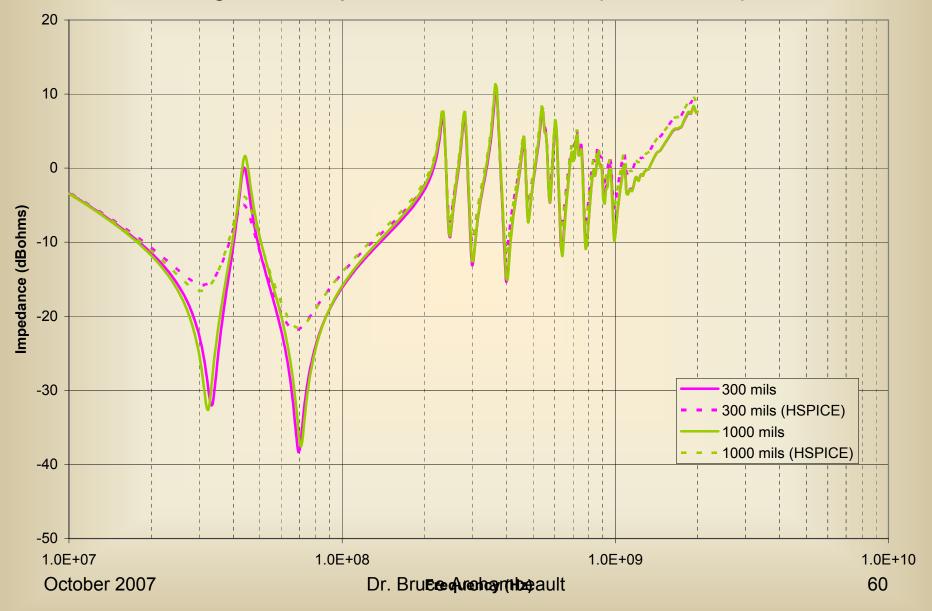

## Impedance Comparison (EZ-PP vs HSPICE) at Port #1 Single 0.01 uF Capacitor at Various Distances (10mil Dielectric)

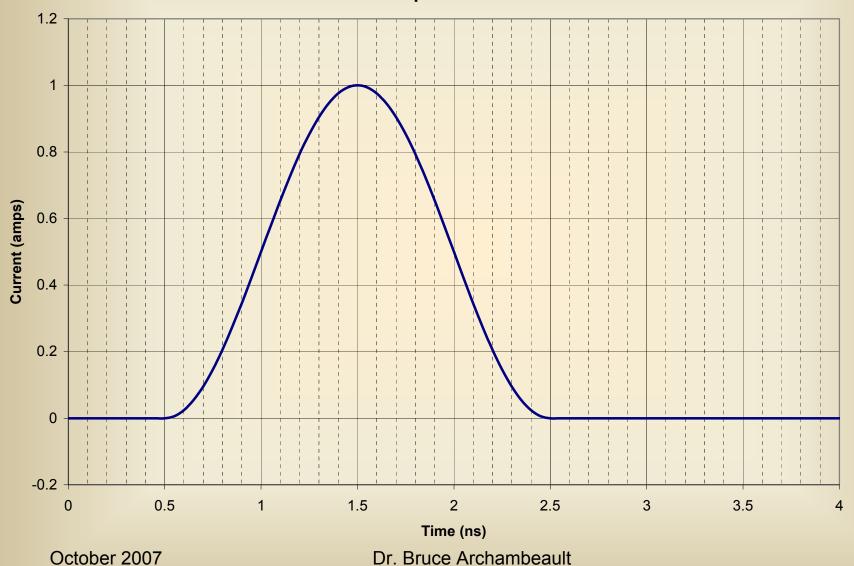

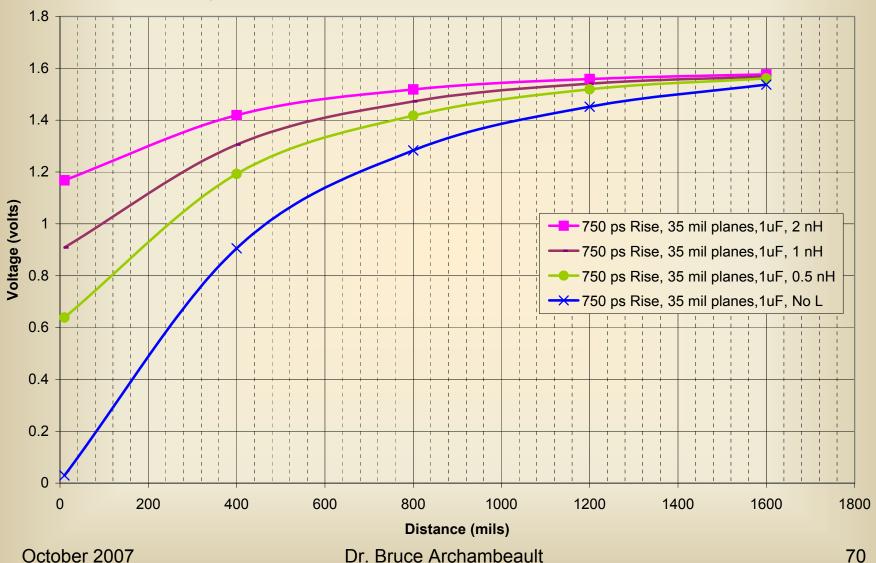

## Current Source Pulse for Simulated IC Power/GND 750 ps Rise/Fall

61

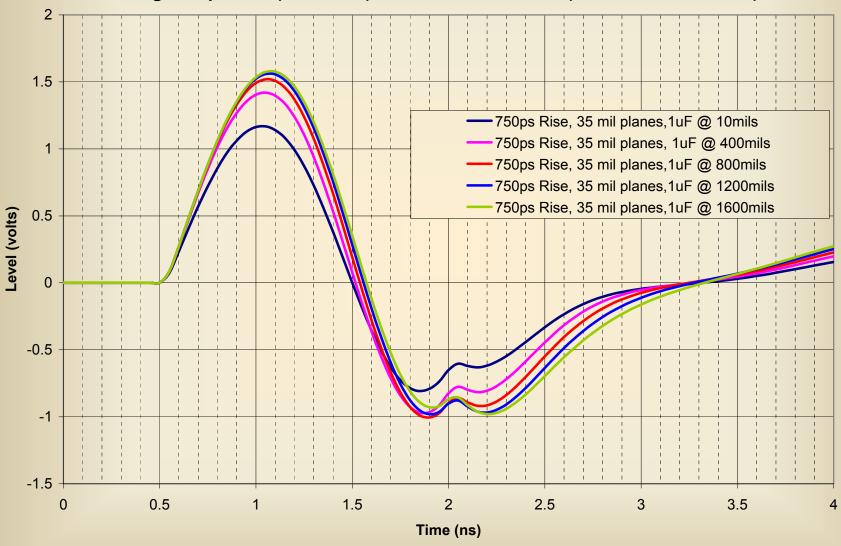

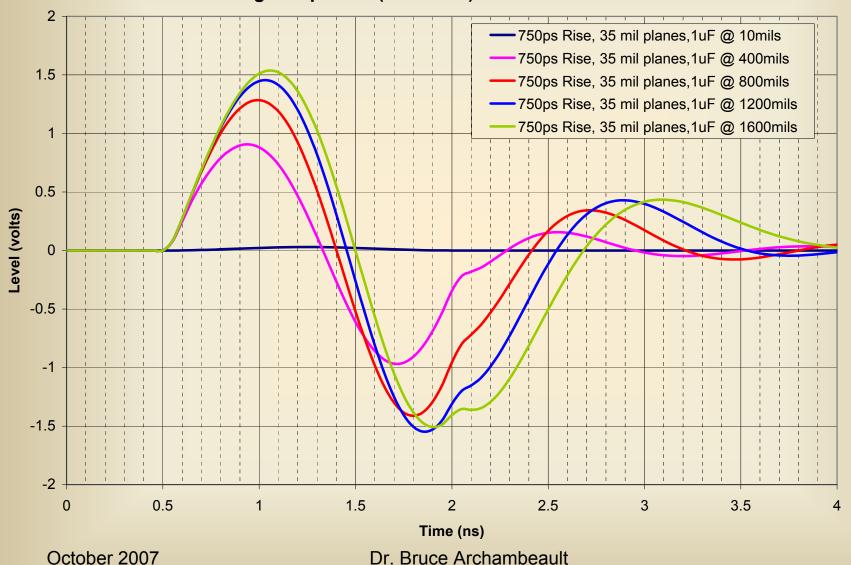

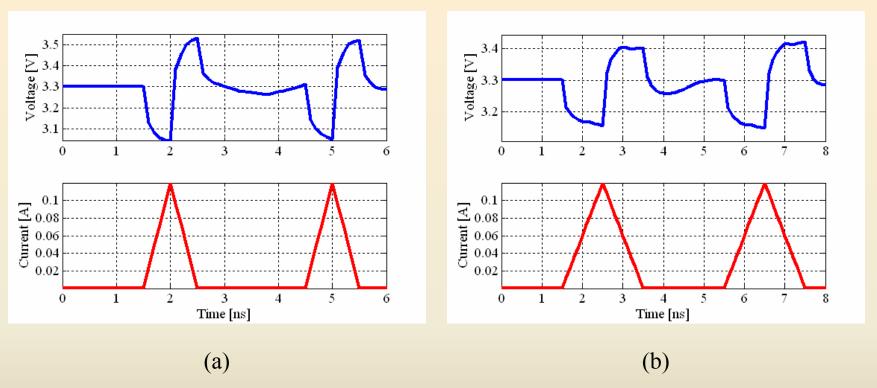

### Time Domain Noise Voltage Across Simulated IC Power/GND Pin (1 amp) Single Capacitor (with 2 nH) at Various Distances (Fullwave Simulation)

Dr. Bruce Archambeault

62

October 2007

### Time Domain Current through Capacitor From Simulated IC Power/GND (1 amp) Single Capacitor (with 2nH) at Various Distances

October 2007

Dr. Bruce Archambeault

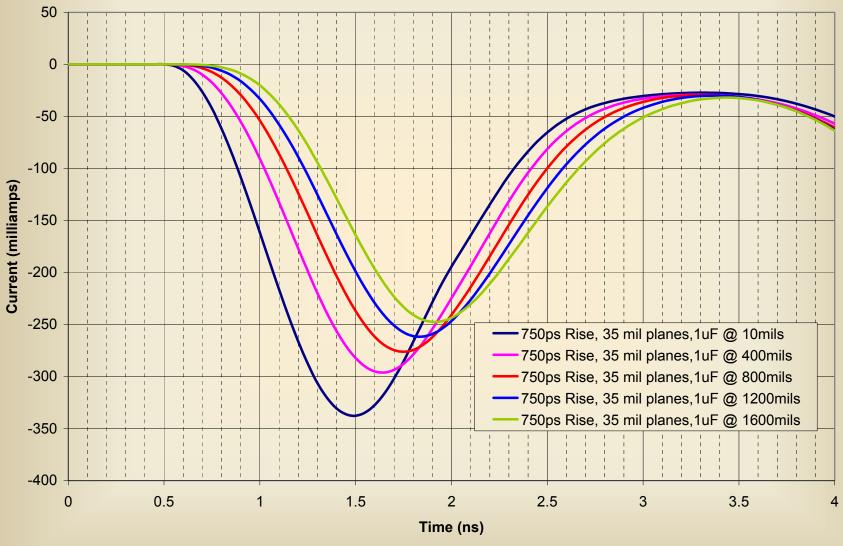

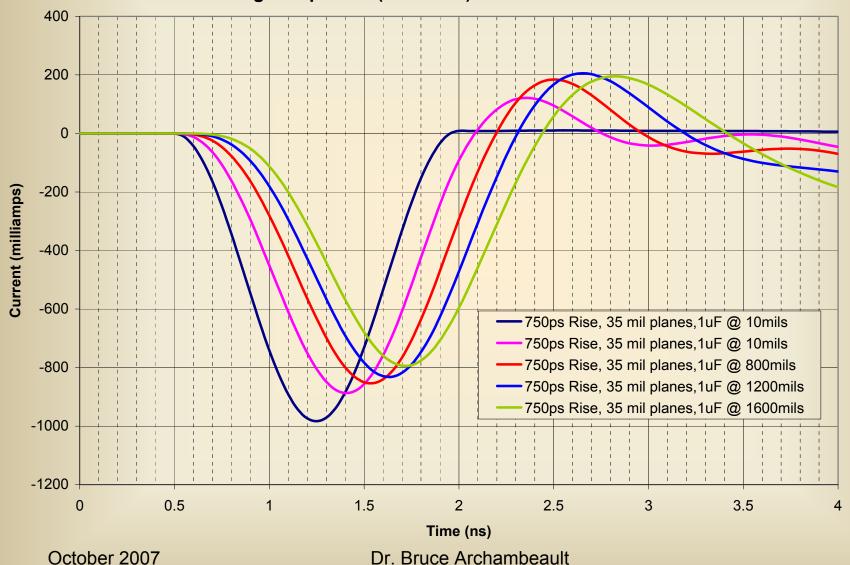

### Time Domain Noise Voltage Across Simulated IC Power/GND Pin (1 amp) Single Capacitor (with No L) at Various Distances

64

### Time Domain Current through Capacitor From Simulated IC Power/GND (1 amp) Single Capacitor (with no L) at Various Distances

65

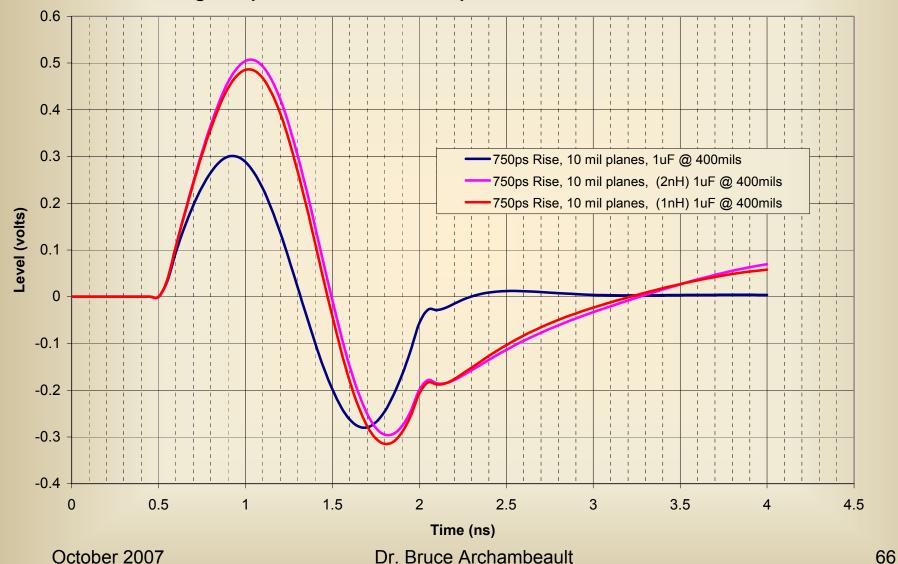

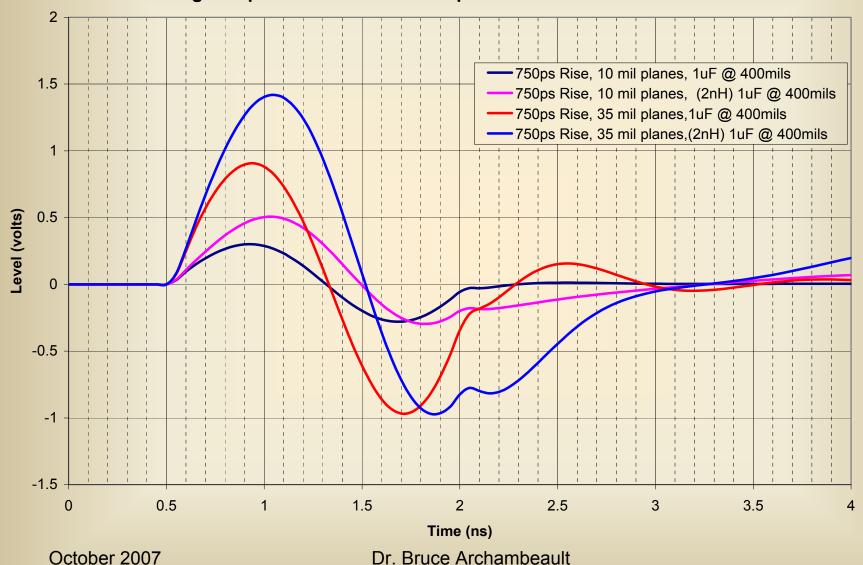

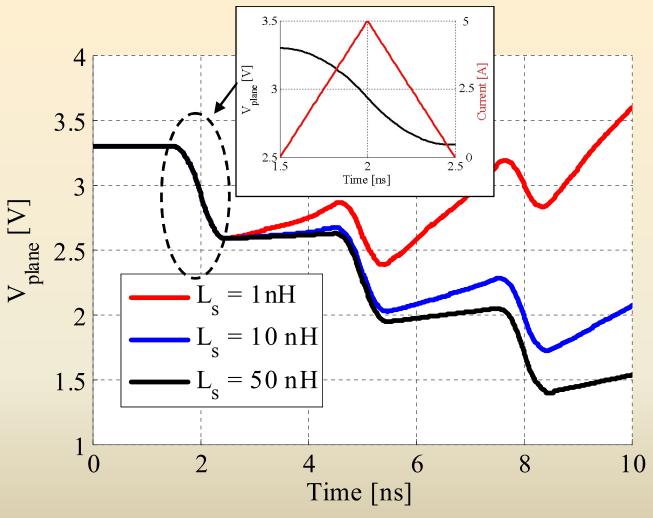

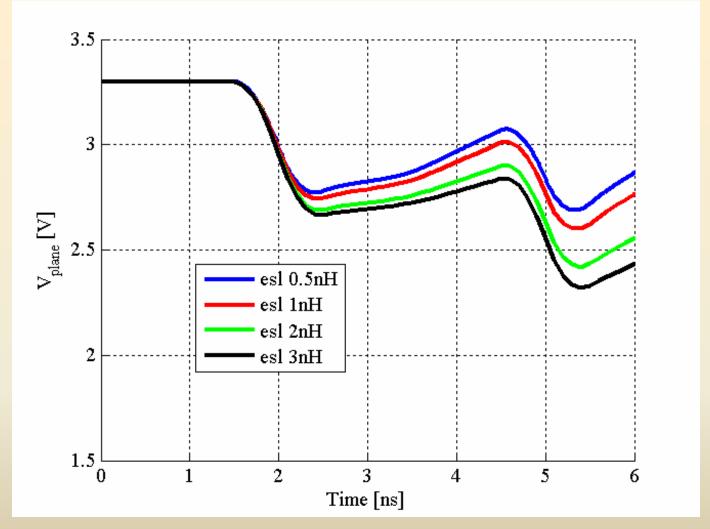

### Time Domain Noise Voltage Across Simulated IC Power/GND Pin (1 amp) Single Capacitor with Various Capacitor Connection Inductance

## Time Domain Noise Voltage Across Simulated IC Power/GND Pin (1 amp) Single Capacitor with Various Capacitor Connection Inductance

67

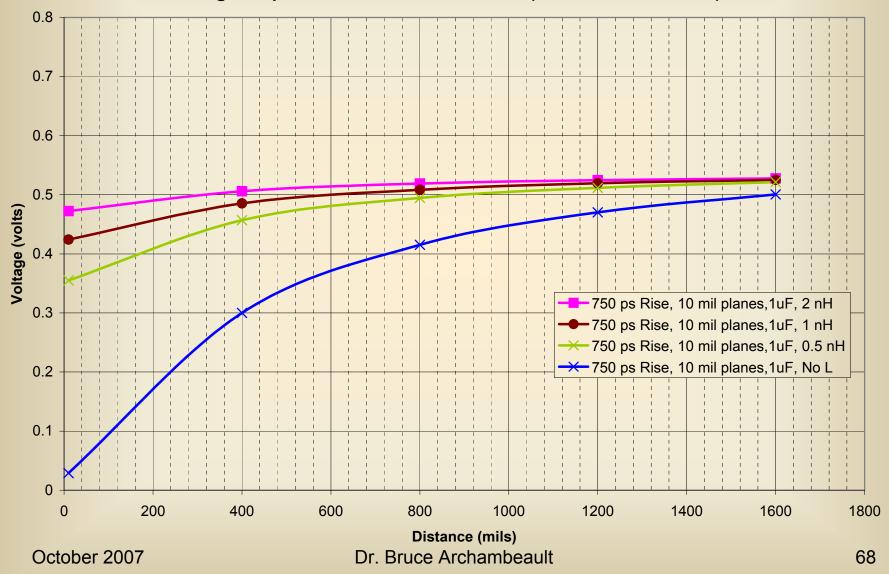

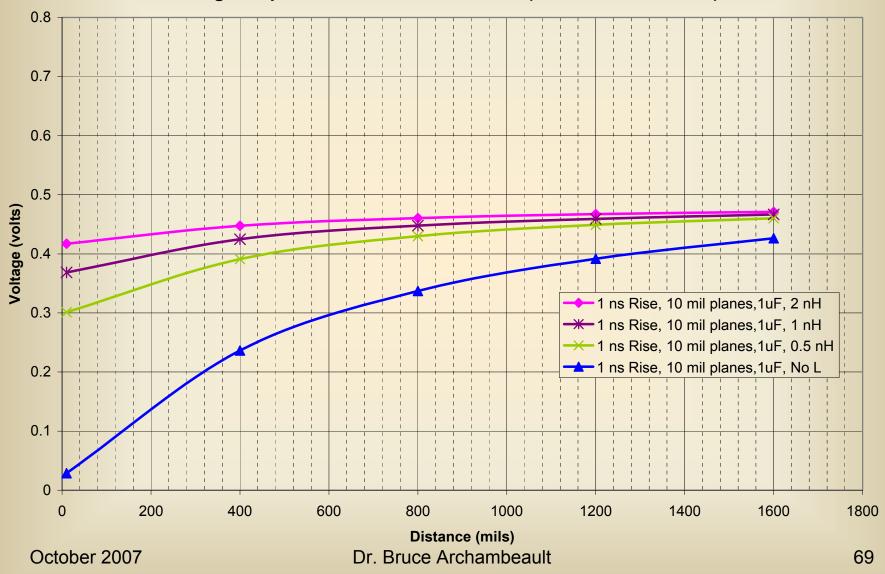

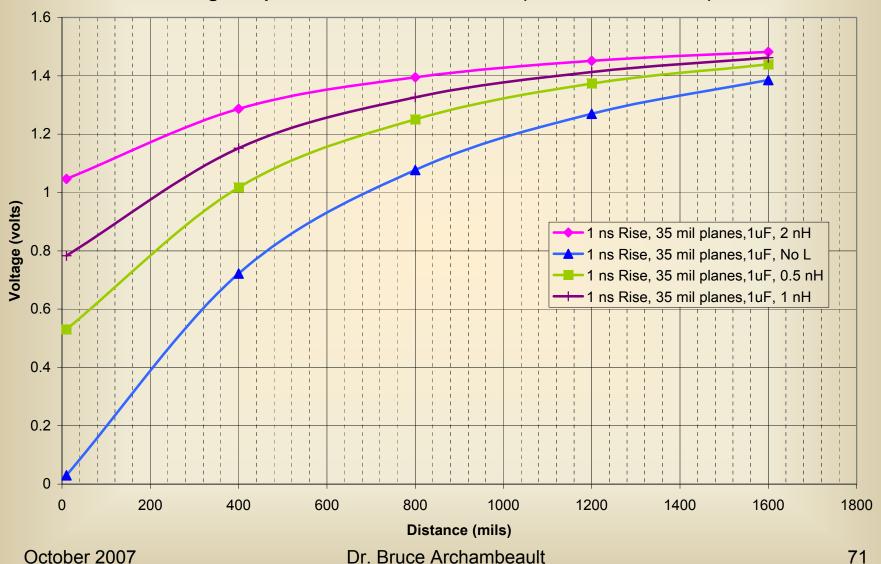

## Maximum Voltage vs Distance to Capacitor for 1 ns Rise/fall time 0.01 uF Capacitor with 0.5 nH ESL and 30 mOhm ESR

#### So Far.....

- Frequency domain simulations not optimum for charge delivery decoupling calculations (phase not considered)

- Time domain simulations using single pulse of current indicate limited capacitor location effect

- Connection inductance of capacitor much higher than inductance between planes

- Charge delivered only from the planes

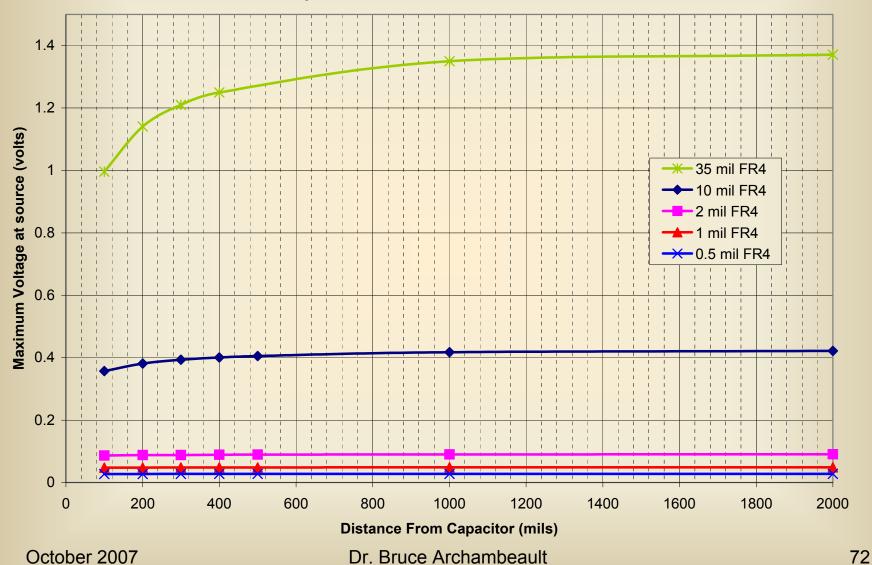

#### Charge Depletion

- IC draws charge from planes

- Capacitors will re-charge planes

- Location <u>does</u> matter!

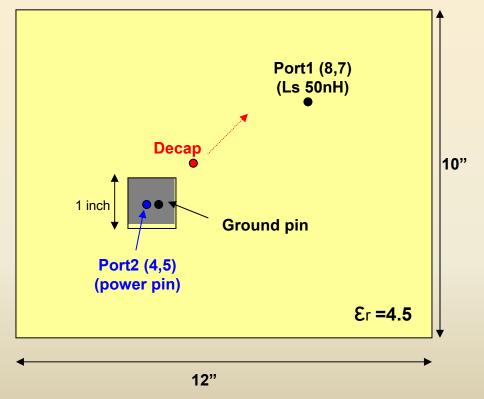

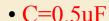

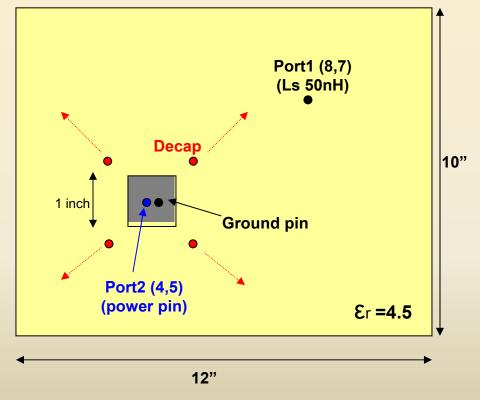

# Model for Plane Recharge Investigations

Port 2 represents IC current draw

# Charge Between Planes vs.. Charge Drawn by IC

Board total charge : C\*V = 3.5nF\*3.3V = 11nC

Pulse charge 5A peak : I\*dt/2 = (1ns\*5A)/2=2.5nC

#### Triangular pulses (5 Amps Peak)

### Noise Voltage from Inductive Effect of Current Draw

Current pulses too small to see charge depletion effects in this time scale

#### Charge Depletion → Voltage Drop

October 2007

Dr. Bruce Archambeault

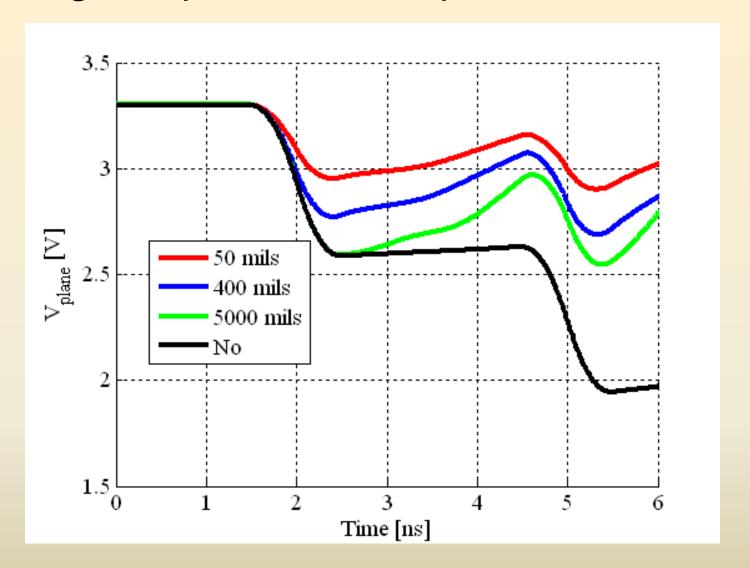

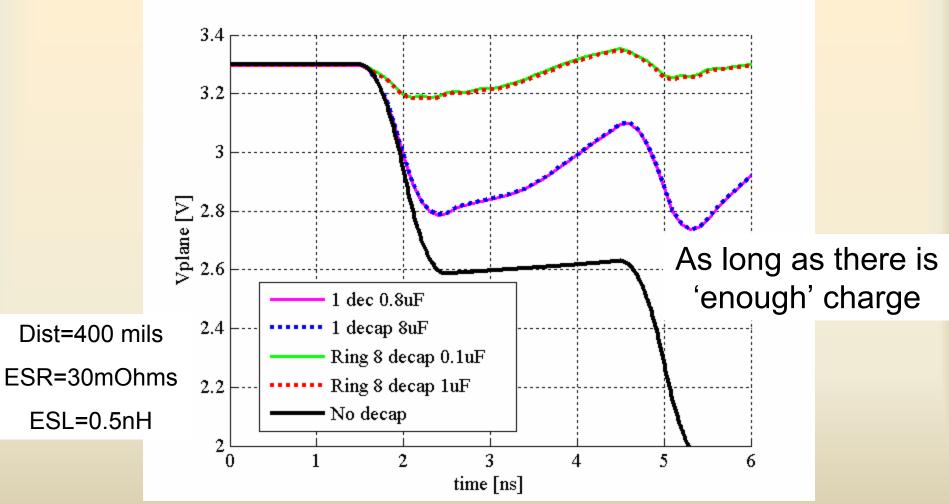

#### Charge Depletion vs. Capacitor Distance

### Charge Depletion for Capacitor @ 400 mils for Various Connection Inductance

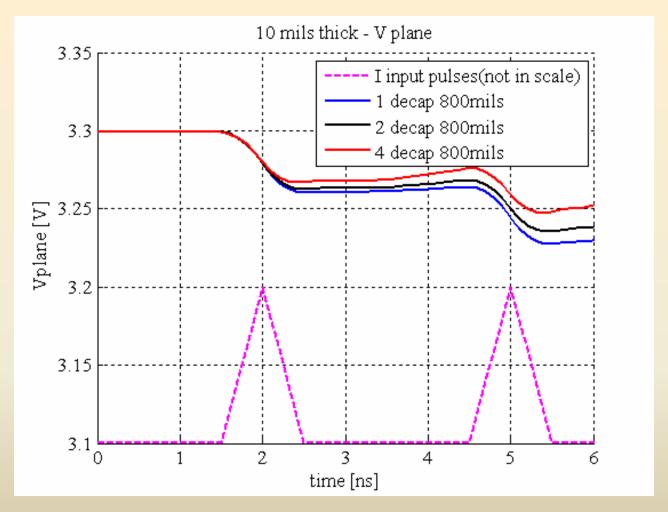

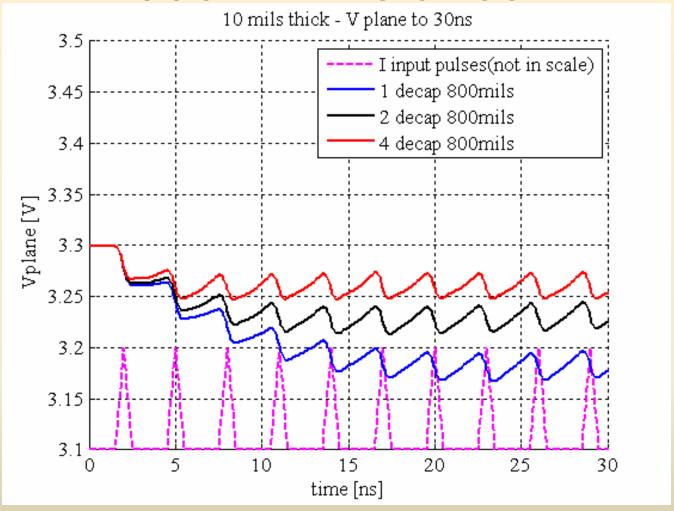

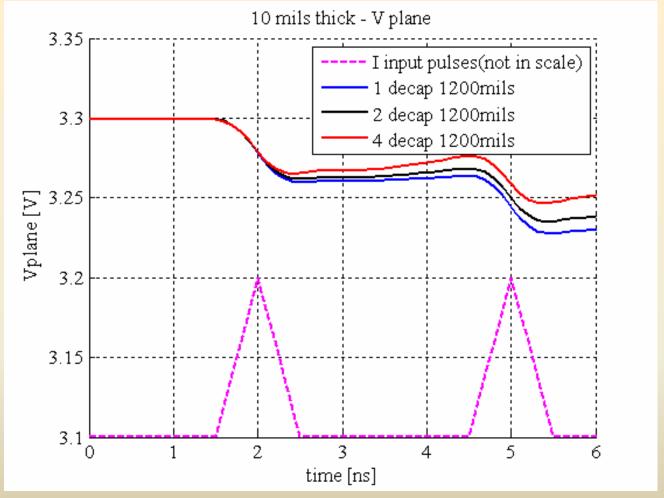

### Effect of Multiple Capacitors While Keeping Total Capacitance Constant

The decap locations are 800mils, 1200mils, 2700mils from the power pin

(power-ground pins at IC center)

- C=1uF

- ESL=0.5nH

- ESR= $1\Omega$

Dr. Bruce Archambeault

#### Effect of Multiple Capacitors While Keeping **Total Capacitance Constant**

The decap locations are 800mils, 1200mils, 2700mils from the power pin

(power-ground pins at IC center)

- ESL=0.5nH

- ESR=1 $\Omega$

Dr. Bruce Archambeault

### Effect of Multiple Capacitors While Keeping Total Capacitance Constant

The decap locations are 800mils, 1200mils, 2700mils from the power pin

(power-ground pins at IC center)

- ESL=0.5nH

- ESR= $1\Omega$

## Constant Capacitance 800 mil Distance

## Constant Capacitance 800 mil Distance

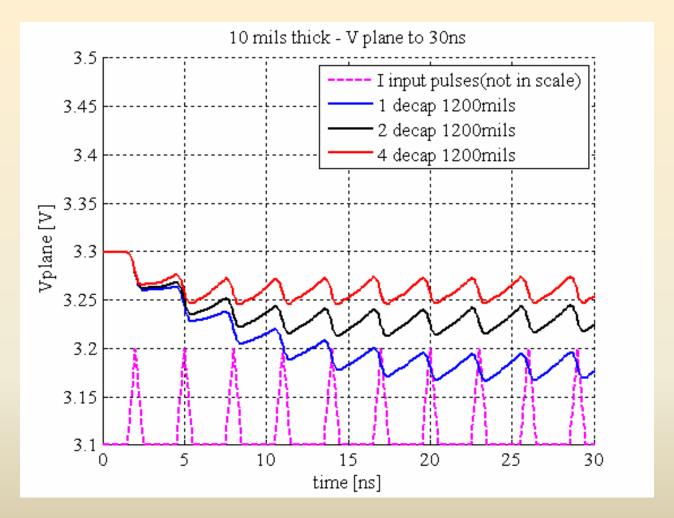

### Constant Capacitance 1200 mil Distance

#### Constant Capacitance 1200 mil Distance

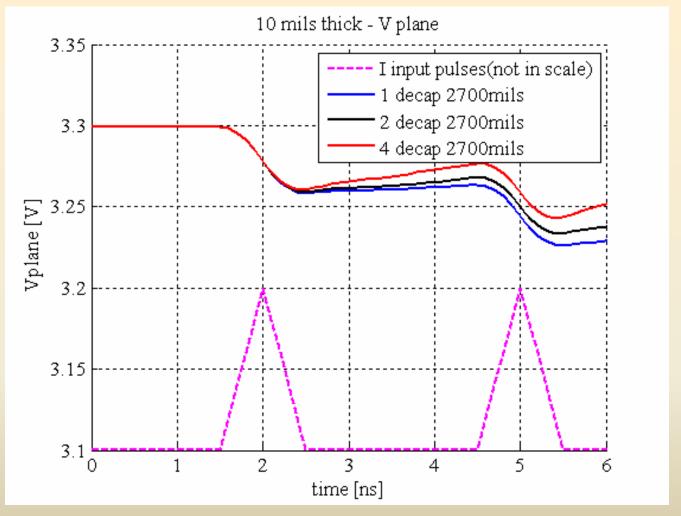

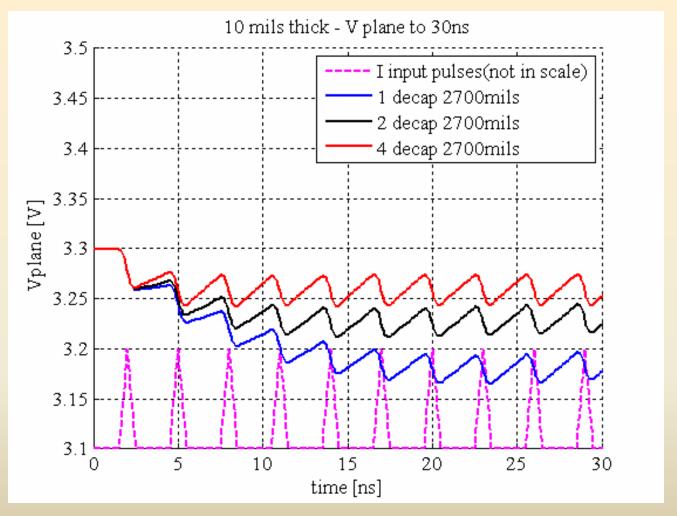

## Constant Capacitance 2700 mil Distance

## Constant Capacitance 2700 mil Distance

# Example #1 Low Cap Connection Inductance

# Example #2 High Cap Connection Inductance

# Example #1 Hi Cap Connection Inductance

# Example #1 Lower Cap Connection Inductance

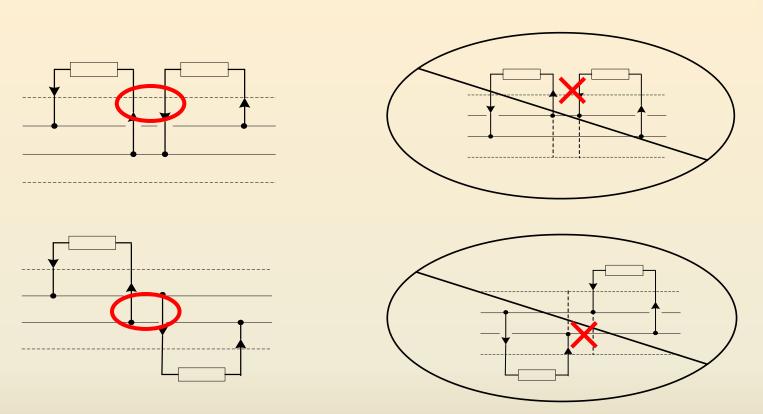

### Mutual Inductance Helps Reduce Path Inductance

Do's Don'ts

J. L Knighten, B. Archambeault, J. Fan, et. al., "PDN Design Strategies: II. Ceramic SMT Decoupling Capacitors – Does Location Matter?," *IEEE EMC Society Newsletter*, Issue No. 207, Winter 2006, pp. 56-67.

#### Effect of Capacitor Value??

- Need enough charge to supply need

- Depends on connection inductance

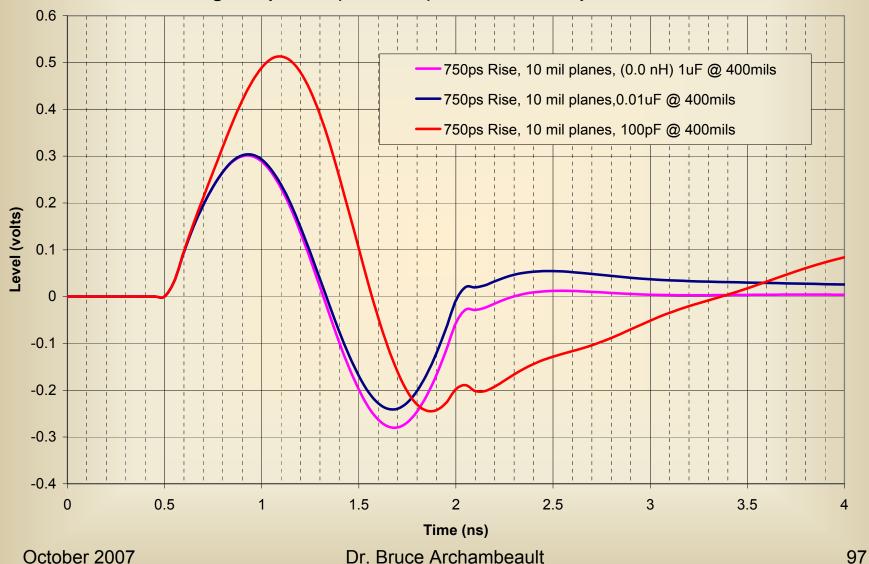

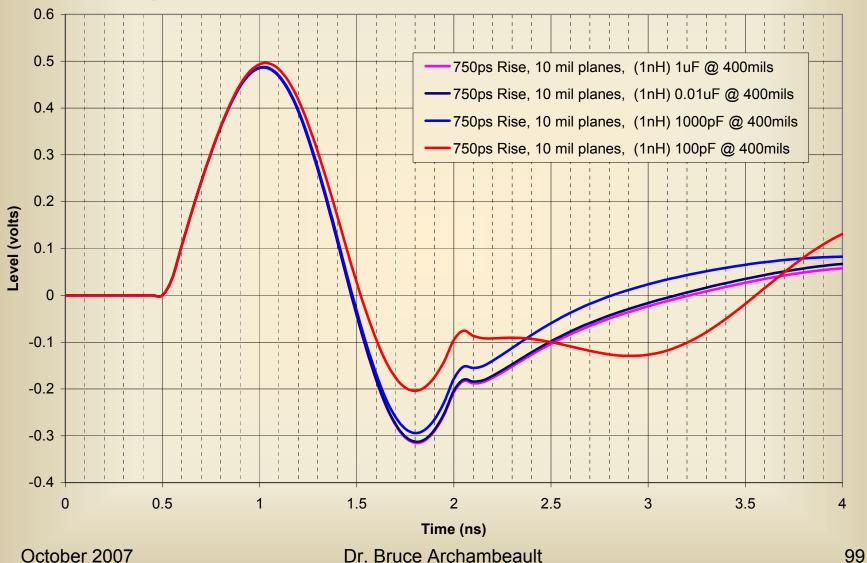

#### Time Domain Noise Voltage Across Simulated IC Power/GND Pin (1 amp) Single Capacitor (with No L) with Various Capacitor Values

#### Time Domain Noise Voltage Across Simulated IC Power/GND Pin (1 amp) Single Capacitor (with 0.5 nH Connection L) with Various Capacitor Values

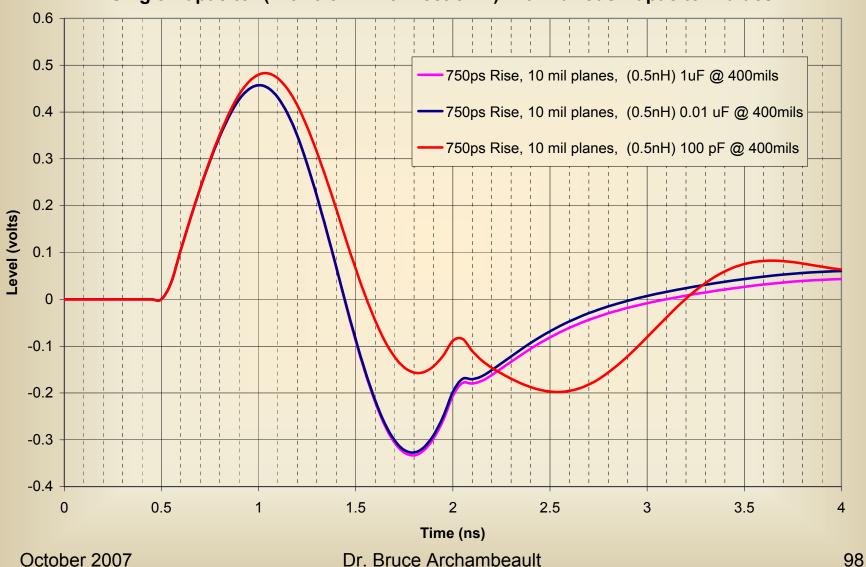

#### Time Domain Noise Voltage Across Simulated IC Power/GND Pin (1 amp) Single Capacitor (with 1 nH Connection L) with Various Capacitor Values

# Noise Voltage is INDEPENDENT of Amount of Capacitance!

Dr. Bruce Archambeault

100

October 2007

#### Decoupling Summary (1)

- EMC Frequency Domain analysis

- Steady-state conditions → resonances

- Transfer function across the board

- Measurements and simulations agree well

- Distance of capacitors from ASIC load does not change steady-state impedance

### Decoupling Summary (2)

- Charge Delivery Time-Limited analysis

- Using equivalent SPICE circuit from simulations

- Current from capacitors change significantly as capacitor moves further away from ASIC

- Noise at ASIC pins increase significantly as capacitor moves further away from ASIC

- Steady-state frequency domain analysis not sufficient for charge delivery design of decoupling capacitors

#### Decoupling Summary (3)

- Recharge the planes

- –Location of Capacitor does matter!

- Effect more significant for thick dielectrics

- Connection Inductance is important

- -Value of capacitance not important

- More capacitors is better than larger/fewer capacitors